| 1 Einführung:                                       | 4  |

|-----------------------------------------------------|----|

| 1.1 Prinzip der Datenverarbeitung                   | 4  |

| 1.1.1 Binäre Daten:                                 | 4  |

| 1.1.2 Verarbeitung binärer Daten                    | 4  |

| 1.2 Blockschaltbild eines Mikrocontrollers          | 5  |

| 1.2.1 Zentraleinheit                                | 5  |

| 1.2.2 Zentralspeicher                               | 6  |

| 1.2.3 Ein-/Ausgabe- Bausteine                       | 6  |

| 1.2.4 Busleitungen                                  |    |

| 1.3 Prinzipieller Ablauf eines Programms            |    |

| 2 Microcontroller der Serie 8051                    |    |

| 2.1 Die Architektur des MAB 8051 AH                 |    |

| 2.1.1 Überblick                                     |    |

| 2.1.2 Speicheraufbau                                |    |

| 2.1.3 Akkumulator                                   |    |

| 2.1.4 Register B                                    | 10 |

| 2.1.5 Programmstatuaregister                        |    |

| 2.1.6 Stack pointer                                 |    |

| 2.1.7 Datenzeiger                                   |    |

| 2.1.8 Ports 0 bis 3                                 |    |

| 2.1.9 Zeitgeber-Register                            |    |

| 2.1.10 Serieller Datenpuffer                        |    |

| 2.1.11 Steuerregister                               |    |

| 3 Überblick über den 80C517/80C517A                 |    |

| 3.1 Speicherorganisation                            |    |

| 3.1.1 Allgemeines                                   |    |

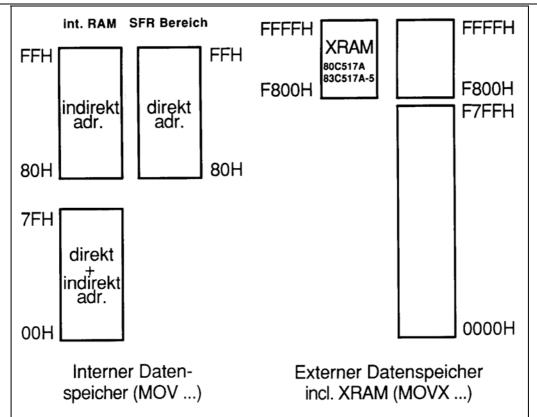

| 3.1.2 Interner Datenspeicher                        |    |

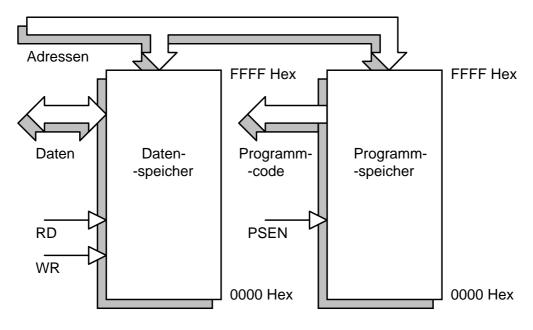

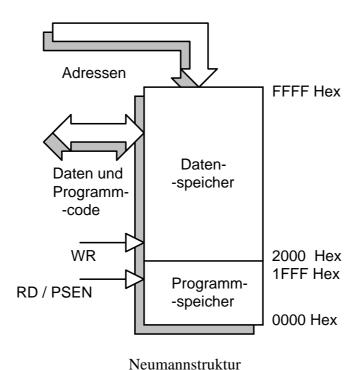

| 3.1.3 Die Code-Data-Struktur des 8051               | 16 |

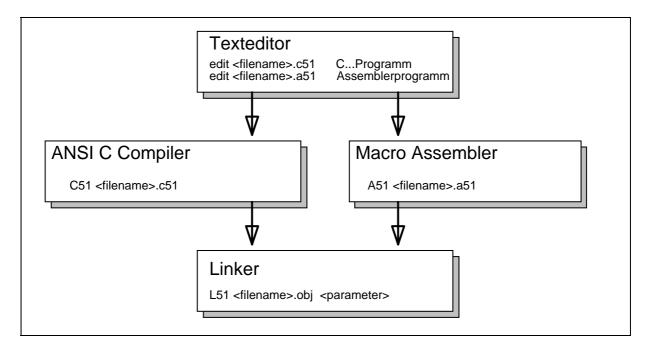

| 4 C-Programme für den 8051                          | 18 |

| 4.1 Allgemeines                                     | 18 |

| 4.2 Zugriff auf Special Function Register           | 18 |

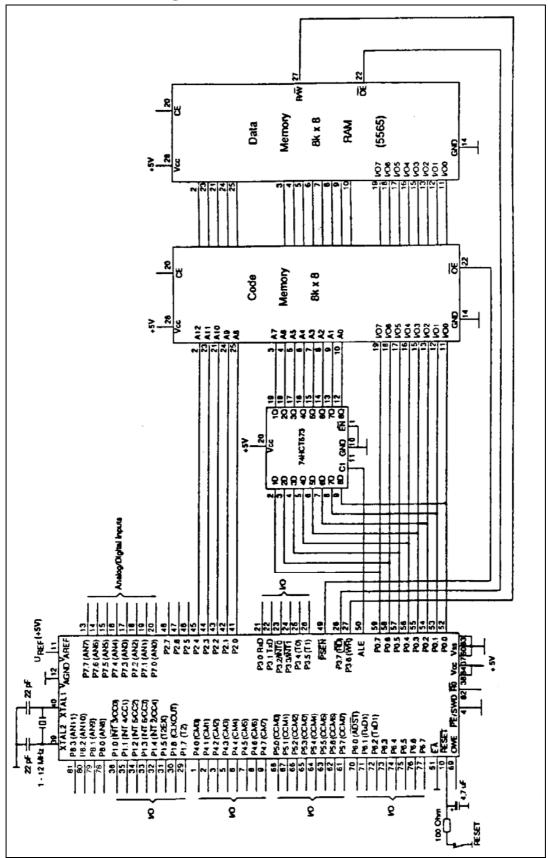

| 5 Standardbeschaltung des Microcontrollers 80C537   |    |

| 6 Serielle Schnittstelle(n)                         | 21 |

| 6.1 RS232-Schnittstelle an einem Personal Computer: | 23 |

| 6.2 Andere serielle Schnittstellen:                 | 24 |

| 6.3 Die seriellen Schnittstellen des 80C517         | 26 |

| 6.3.1 Serielle Schnittstelle 0                      | 26 |

| 6.3.2 Serielle Schnittstelle 1:                     | 29 |

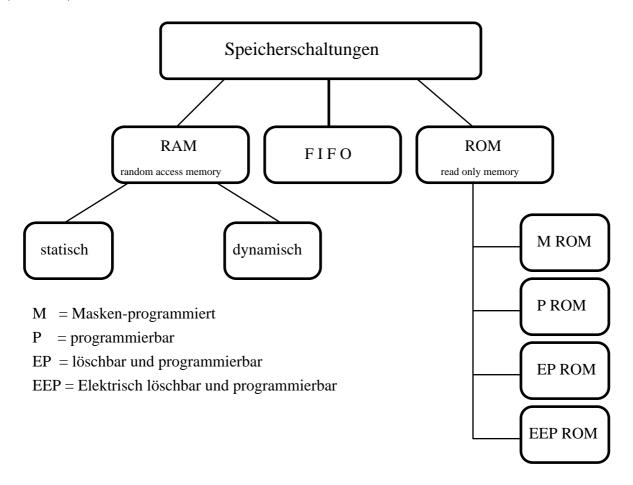

| 7 Speicher                                          | 31 |

| 7.1 Allgemeines                                     |    |

| 7.2 Speicherorganisation:                           | 32 |

| 7.3 Statische RAMs:                                 | 33 |

| 7.3.1 TTL-Speicherzelle:                            | 33 |

| 7.3.2 CMOS-Speicherzelle:                           | 35 |

| 7.3.3 Symbole für Impuls- bzw. Zeitdiagramme:       | 36 |

| 7.3.4 Zeitbedingungen:                              |    |

| 7.3.5 Beispiel aus dem Datenbuch:                   |    |

| 7.4 Dynamische RAMs:                                |    |

| 7.4.1 Speicherzellenaufbau:                         | 40 |

| 7.4.2 Dynamic RAM Controller:                       | 41 |

|                                                     |    |

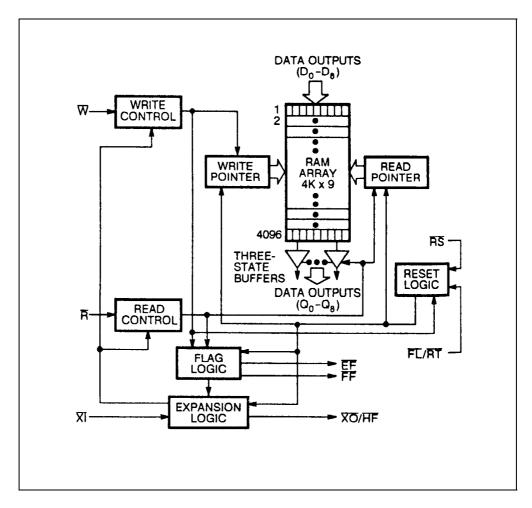

| 7.5 FIFO-Speicher (First In First Out Memories)               | 45 |

|---------------------------------------------------------------|----|

| 7.6 Festwertspeicher (ROM)                                    | 45 |

| 7.6.1 Masken-ROMs:                                            | 46 |

| 7.6.2 PROM (Programmierbare Festwertspeicher):                | 46 |

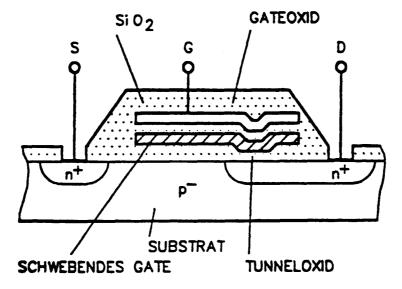

| 7.7 UV-löschbare Festwertspeicher (EPROM):                    | 47 |

| 7.8 Elektrisch löschbare Festwertspeicher (EEPROMs):          | 49 |

| 7.9 Flash-EEPROMs:                                            |    |

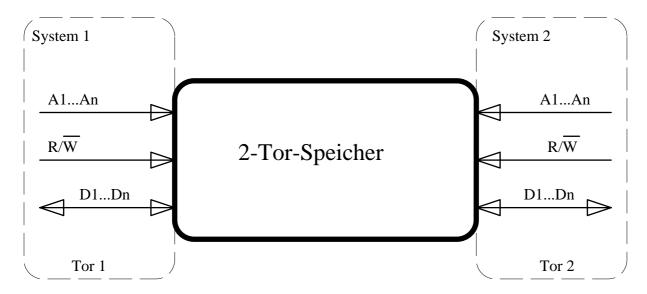

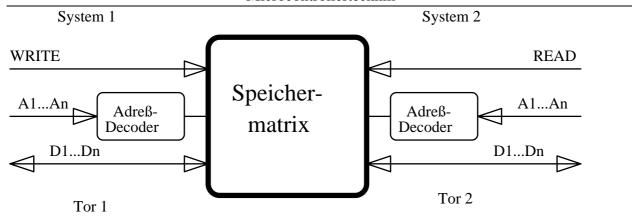

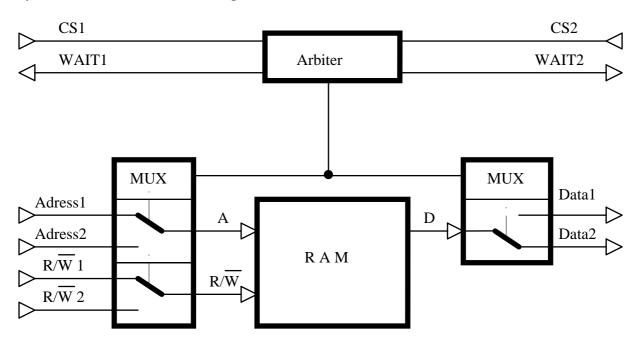

| 7.10 Zweitorspeicher:                                         | 50 |

| 8 Anschluß eines LCDs                                         | 52 |

| 8.1 Allgemeines                                               |    |

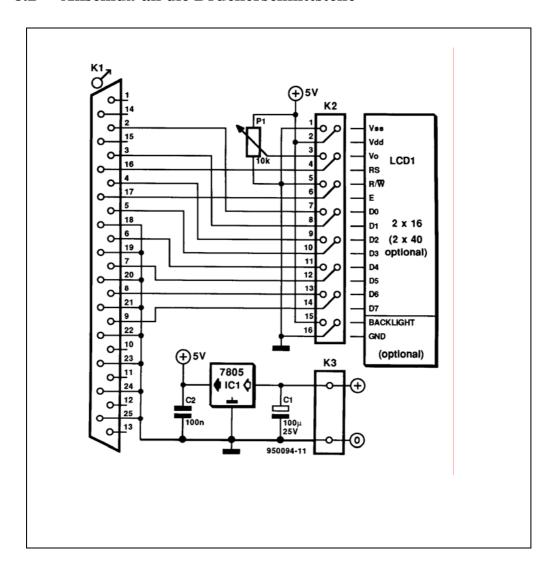

| 8.2 Anschluß an die Druckerschnittstelle                      |    |

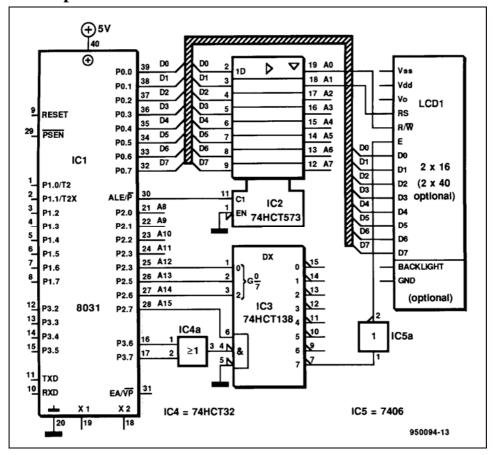

| 8.3 Beispiel für den Anschluß an einen 8031er Adresse F000H:  |    |

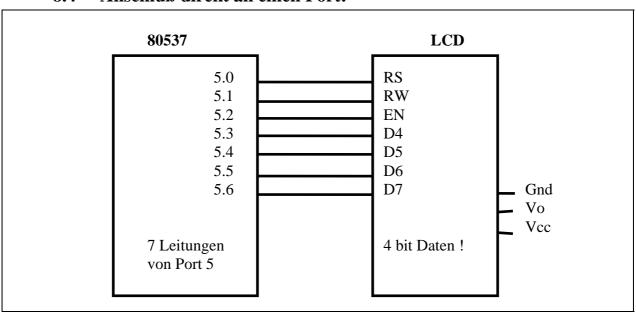

| 8.4 Anschluß direkt an einen Port:                            |    |

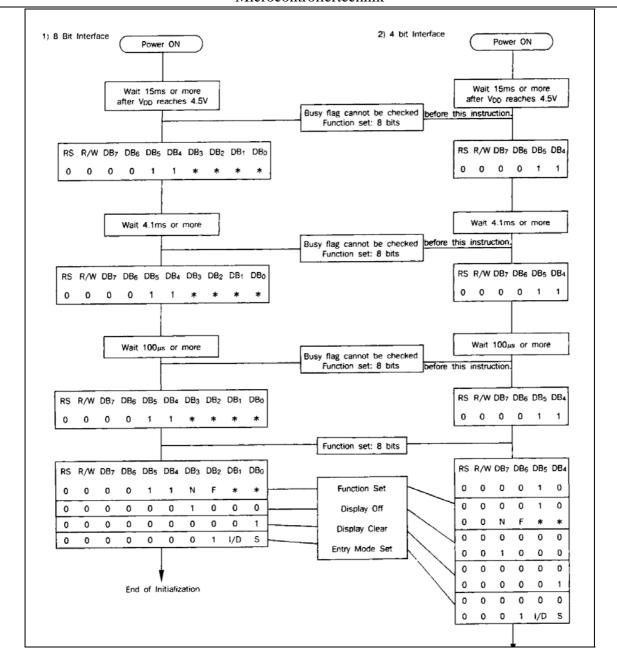

| 8.5 Befehlssatz                                               |    |

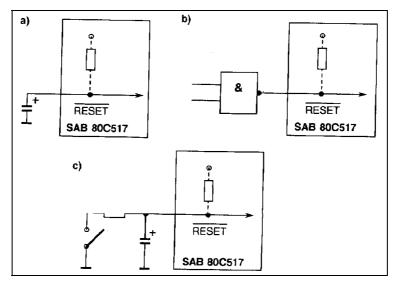

| 9 Reset                                                       |    |

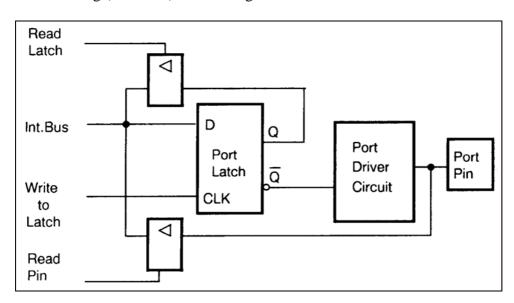

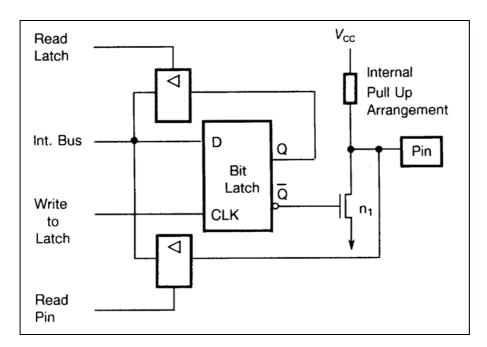

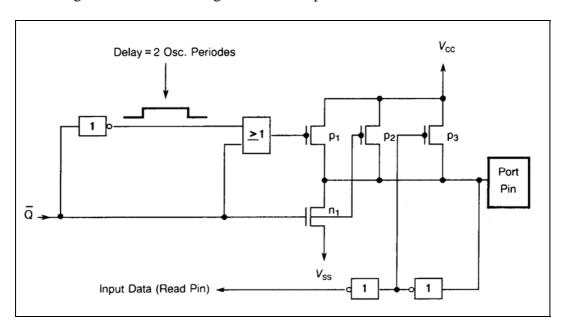

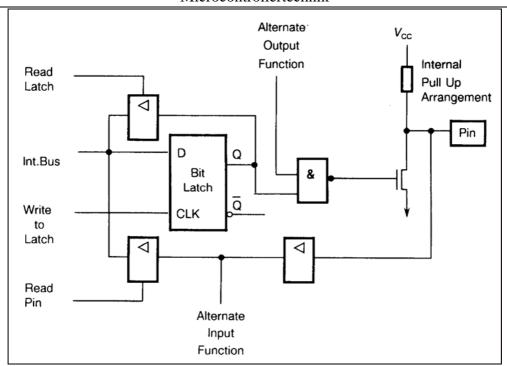

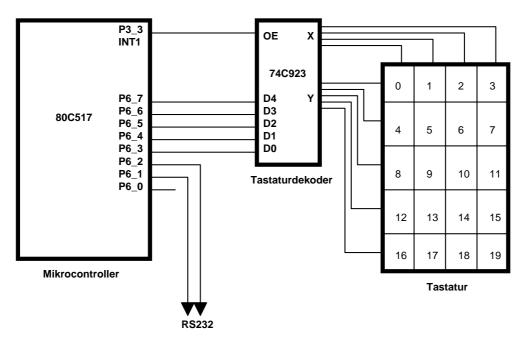

| 10 Parallele Eingabe-Ausgabe-Ports                            |    |

| 10.1 Digitale Ein-Ausgabe-Ports                               |    |

| 10.2 Analog/Digitale Eingabeports                             |    |

| 10.3 Alternative Port-Funktionen                              | 62 |

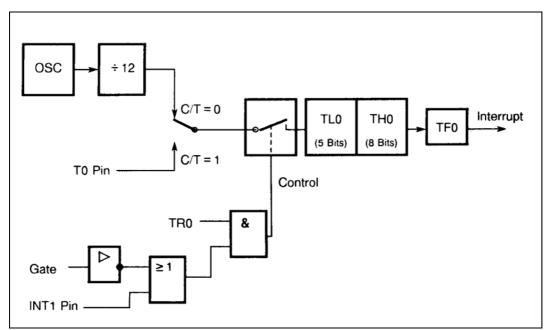

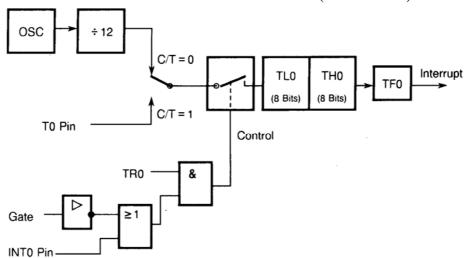

| 11 Timer                                                      |    |

| 11.1 Modus 0                                                  |    |

| 11.2 Modus 1                                                  |    |

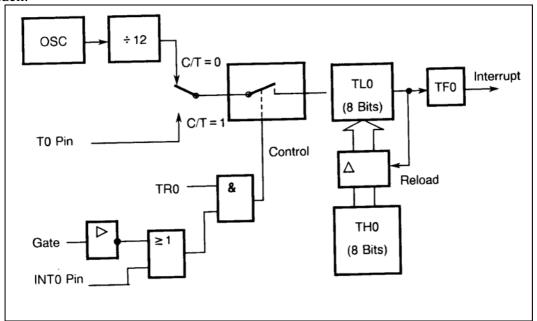

| 11.3 Modus 2                                                  |    |

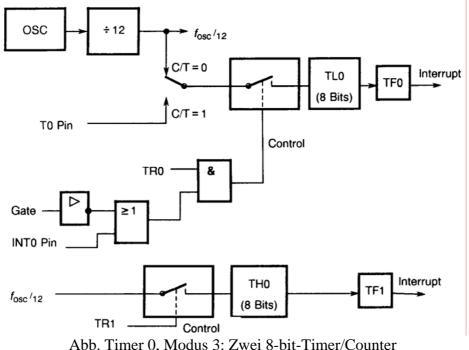

| 11.4 Modus 3                                                  |    |

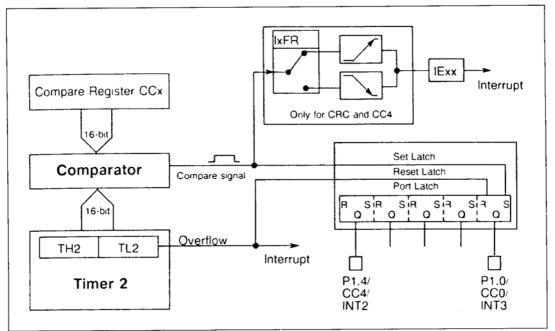

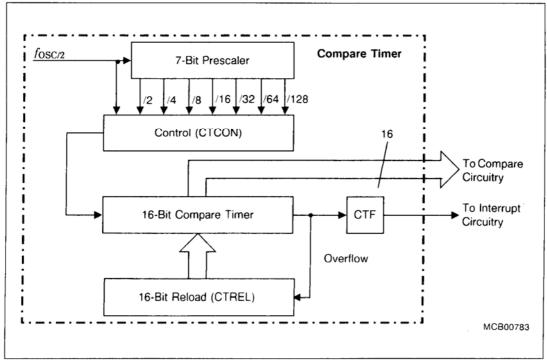

| 12 Capture/Compare-Einheit                                    |    |

| 12.1 Begriffserklärung                                        |    |

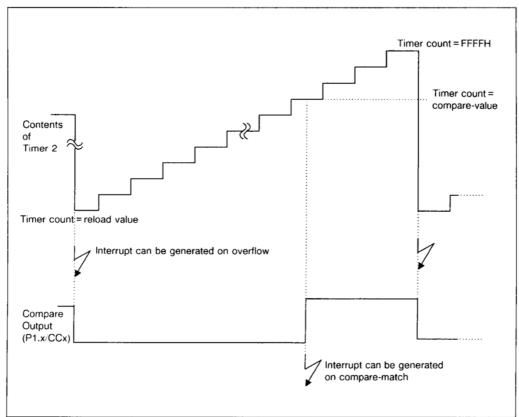

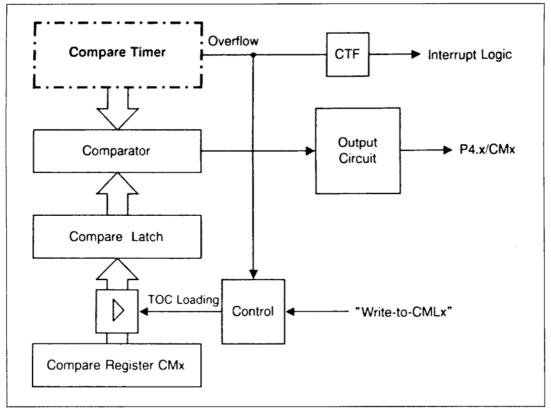

| 12.1.1 Compare                                                |    |

| 12.1.2 Reload                                                 |    |

| 12.1.3 Capture                                                |    |

| 12.2 Anwendungsbeispiel PWM                                   |    |

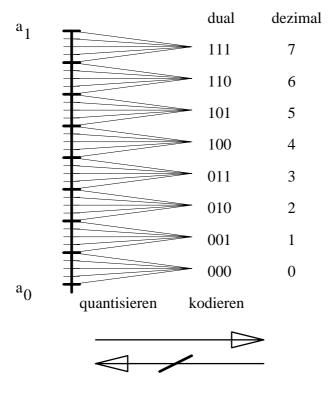

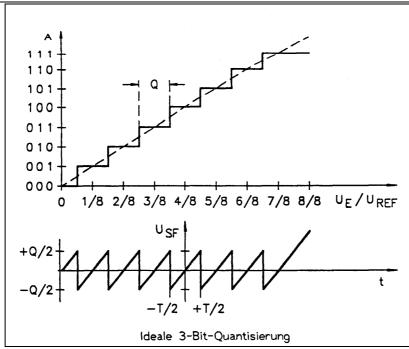

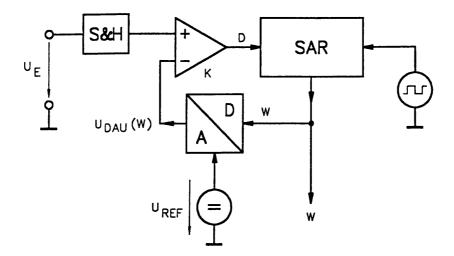

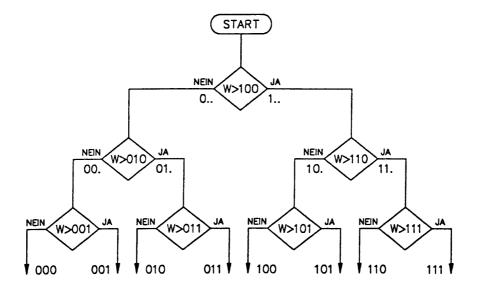

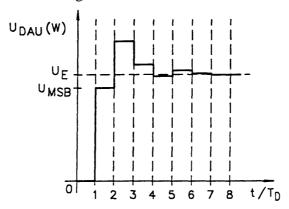

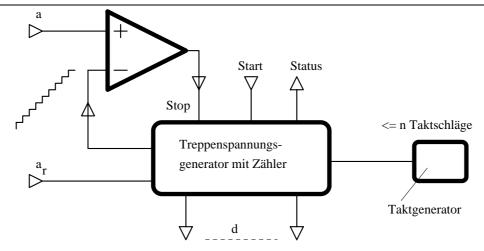

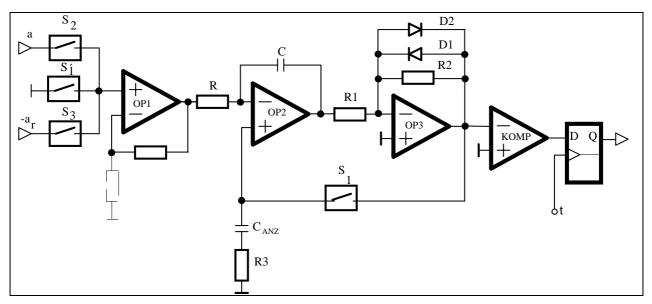

| 13 Analog - Digital - Umsetzer                                |    |

| 13.1 Allgemeines                                              |    |

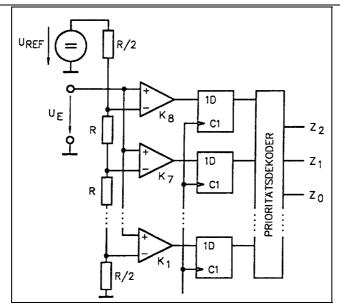

| 13.1.1 Parallelverfahren (flash converter):                   |    |

| 13.1.2 Wägeverfahren (successive approximation)               |    |

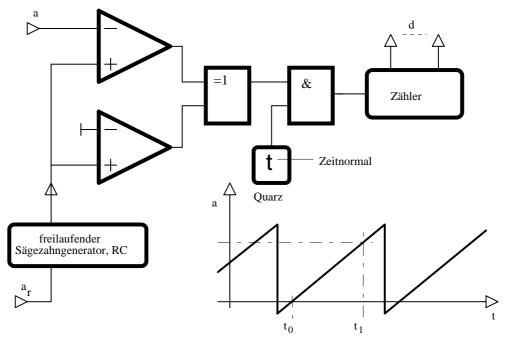

| 13.1.3 Zählverfahren (incremental converter)                  |    |

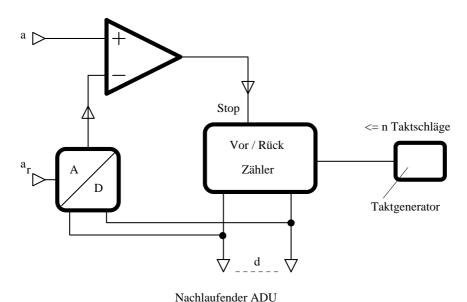

| 13.1.4 Tracking ADC (Nachlaufender ADU):                      |    |

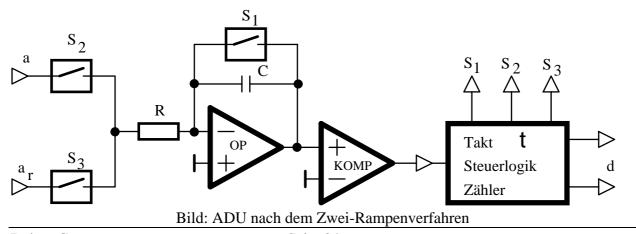

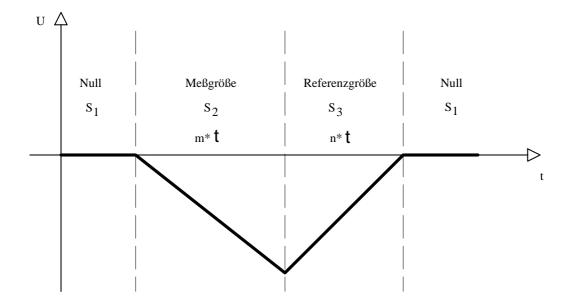

| 13.1.5 Zwei-Rampenverfahren (dual slop, dual ramp):           |    |

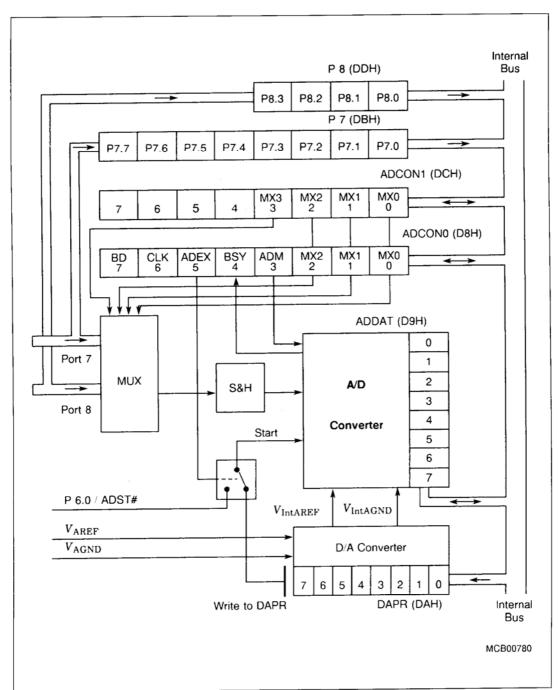

| 13.2 Der ADU des 80C517                                       |    |

| 13.3 Erklärungen                                              |    |

| 13.4 Blockschaltbild ADU 80C517                               |    |

| 13.5 Initialisierung und Wahl des Eingangskanals              |    |

| 13.6 Erhöhung der Umsetzerauflösung von 8 Bit auf 10 Bit:     |    |

| 13.7 Anpassen der Referenzspannungen an die Eingangsspannung: |    |

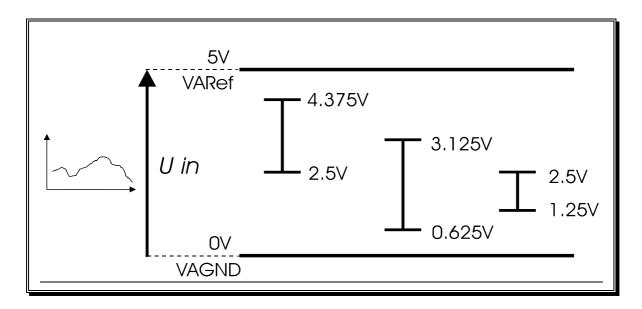

| 13.7.1 Interne einstellbare Referenzspannungen:               |    |

| 14 1 Westelder Timer (WDT)                                    |    |

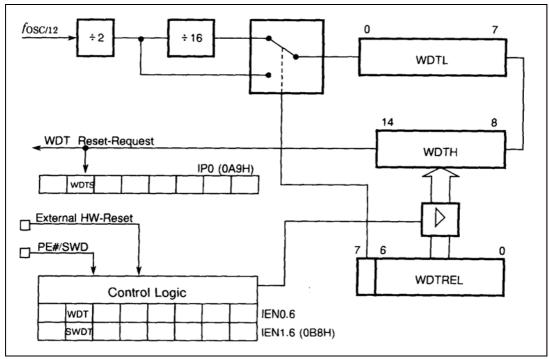

| 14.1 Watchdog-Timer (WDT)                                     |    |

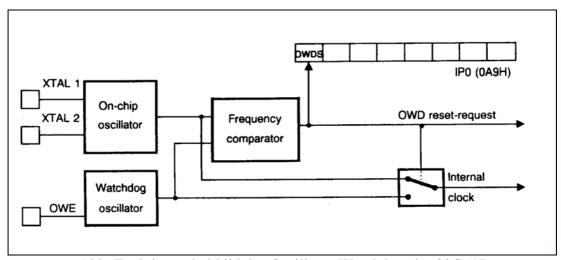

| 14.2 Oszillator-Watchdog (OWD)                                |    |

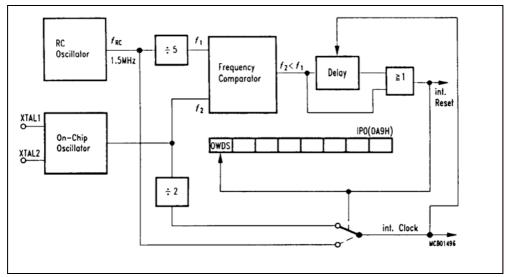

| 14.4 Oszillator-Watchdog im 80C517                            |    |

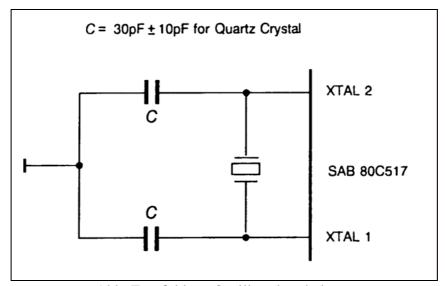

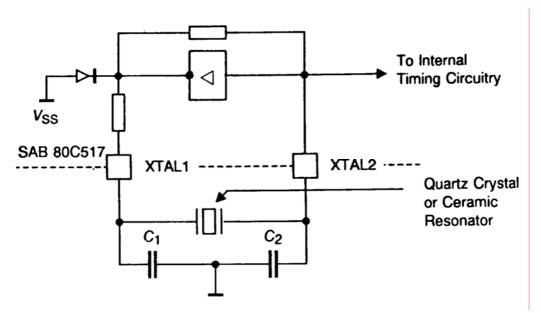

| 15 Oszillator und Taktversorgung                              |    |

| 13 OSZINAWI UNU TAKWCISUIGUNG                                 |    |

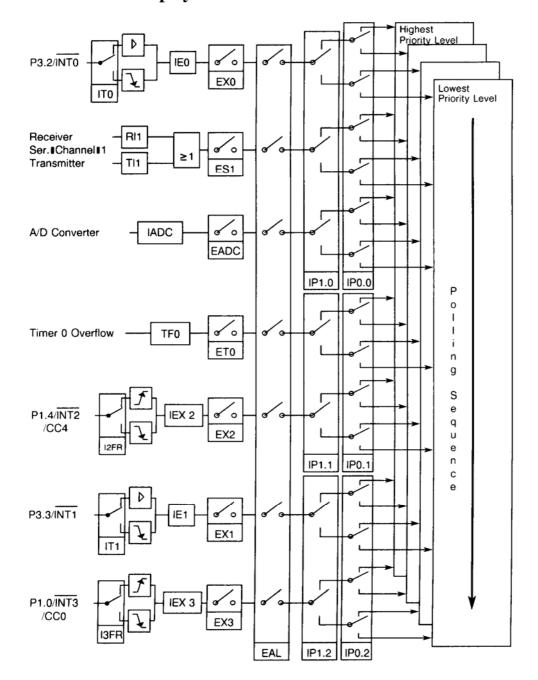

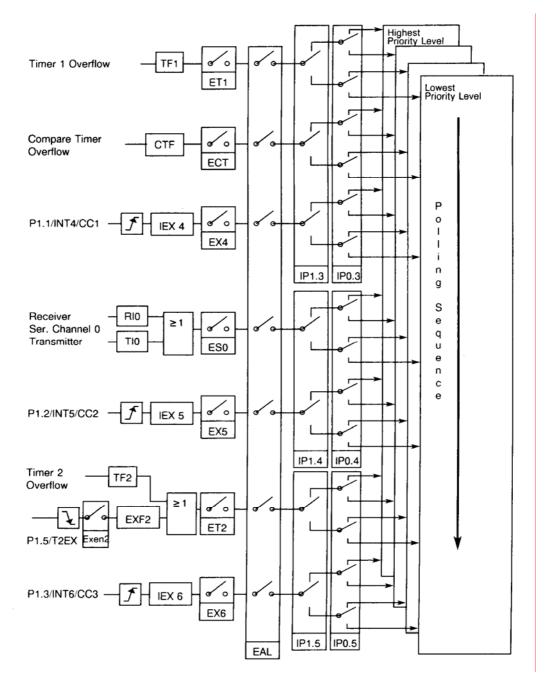

| 16 Interruptsystem                             | 99  |

|------------------------------------------------|-----|

| 16.1 Einlesen eines Ports                      | 99  |

| 16.2 Das Polling Verfahren                     | 99  |

| 16.3 Die Programmierung von Interrupt Routinen |     |

| 16.3.1 Allgemeines                             |     |

| 16.4 Vektoradressen                            | 100 |

| 16.5 Interruptsystem 80C517                    | 101 |

| 16.6 Special Function Register für Interrupts  |     |

| 16.7 Prioritätssteuerung                       |     |

| 16.8 Eine Interruptgesteuerte Zeitschleife     |     |

| 16.9 Interruptquellen und -nummern             |     |

| 17 Literaturnachweis                           |     |

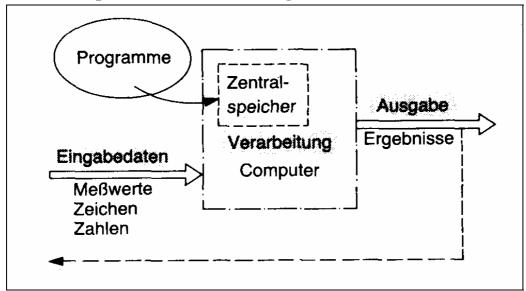

### 1 Einführung

### 1.1 Prinzip der Datenverarbeitung

**Eingabe:** Eingabegeräte stellen Daten zur Verarbeitung bereit

Beispiele: Sensoren, Taster, Datenspeicher, Bussystem

Verarbeitung: Diese Daten werden nun von der eigentlichen Verarbeitungs-

einheit, dem Computer, gelesen und entsprechend einer im Computer

vorhandenen Arbeitsanweisung, dem Programm, verarbeitet.

**Ausgabe:** Die Ergebnisse dieser Verarbeitung müssen ausgegeben werden.

Beispiele: Speicher, Display, Bussystem, Drucker, Steuerelektronik

#### 1.1.1 Binäre Daten

Die Daten werden in binärer Form verarbeitet, d.h. analoge Signale müssen zur weiteren Verarbeitung erst in digitale Signale umgeformt werden. Die digitale Verarbeitung hat sich aus mehreren Gründen durchgesetzt:

- → Daten, z.B. analoge Meßdaten, können nur in digitalisierter Form über längere Zeit gespeichert werden.

- → Die Genauigkeit der Verarbeitung kann man mit relativ geringem Aufwand praktisch beliebig steigern.

- → Digitalisierte Daten sind bei Übertragung störunempfindlicher als analoge Signale.

### 1.1.2 Verarbeitung binärer Daten

Bei einem Computer handelt es sich nicht um eine Schaltung, die speziell für eine bestimmte Aufgabe konstruiert ist (wie GAL), sondern um eine universelle binäre Schaltung, die eingelesene Daten entsprechend den Befehlen des im Computer gespeicherten Programms bearbeiten.

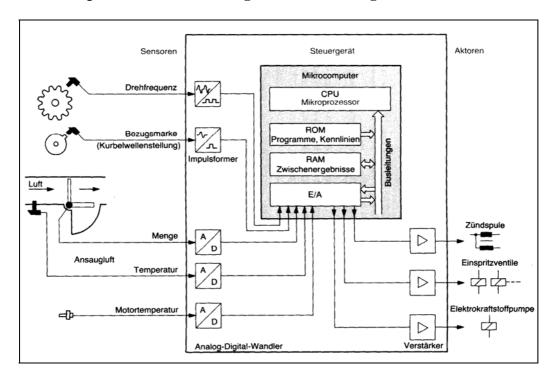

Beispiel: Datenverarbeitung bei der Steuerung eines Ottomotors

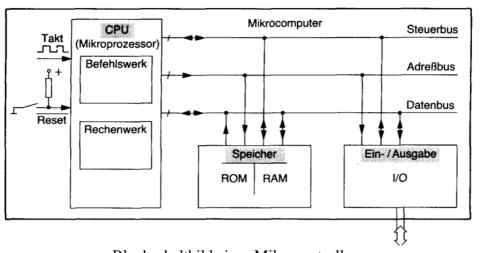

### 1.2 Blockschaltbild eines Mikrocontrollers

Jeder digital arbeitende Computer besteht aus 3 Baugruppen

- → Zentraleinheit (Central Processing Init, CPU)

- → Zentralspeicher (Memory)

- → Ein-/Ausgabe Einheiten (Input/Output, I/O)

#### 1.2.1 Zentraleinheit

Die CPU hat zwei Aufgaben:

- a) Sie steuert den gesamten Ablauf

- b) Sie bearbeitet Daten, kann also arithmetische und logische Operationen

ausführen.

Blockschaltbild eines Mikrocontrollers

Bulme Graz

#### 1.2.2 Zentralspeicher

Zentralspeicher werden von der CPU direkt angesteuert, im Gegensatz zu peripheren Speichern, z.B. Festplatten, Disketten, Bussysteme, die über spezielle E/A Bausteine angesteuert werden müssen.

### **→**Nichtflüchtige Speicher

(Non Volatile Memory) behalten ihre Information auch beim Ausschalten der Versorgungsspannung. Sie sind geeignet für Programme, Codetabellen usw. (Bausteine: ROM, EPROM, EEPROM)

### →Flüchtige Speicher

verlieren ihre Information beim Ausschalten der Versorgungsspannung, dafür lassen sie sich einfach ändern. Sie werden zum Zwischenspeichern von Eingabedaten und Ergebnissen benötigt.

(Bausteine: RAM (Random Access Memory), FIFO (First in first out) und LIFO)

#### 1.2.3 Ein-/Ausgabe- Bausteine

Sie stellen die Verbindung zur Außenwelt des Computers, zur Peripherie, her. Sie werden oft als Ports bezeichnet.

### 1.2.4 Busleitungen

Der Bus besteht aus mehreren Leitungen, wobei an jede Leitunge parallel mehrere Bausteine angeschlossen sind. Zur korrekten Abwicklung des Datenflusses werden im Systembus eines Computers entsprechnd ihrer Aufgabe drei Gruppen von Busleitungen unterschieden:

- a) **Datenbus**

- b) Adreßbus

- c) Steuerbus

Da an einer Datenleitung immer mehrere Sender angeschlossen sind, spricht man hier von einem bidirektionalen Bus.

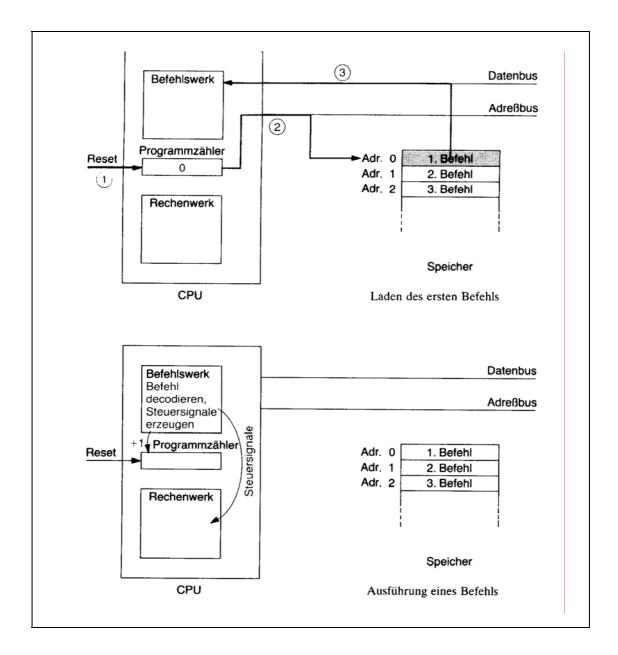

# 1.3 Prinzipieller Ablauf eines Programms

Prinzipieller Ablauf eines Programms in einem Mikrokontrollersystem

### 2 Microcontroller der Serie 8051

Als Mikrocontroller bezeichnet man Integrierte Schaltungen, die auf einem einzigen Chip ein vollständiges Mikrocomputersystem enthalten.

Mikrocontroller werden verwendet, um Regelungen und Steuerungen aufzubauen, um mechanische Aktoren zu bedienen, Sensoren einzulesen und Echtzeitberechnungen durchzuführen.

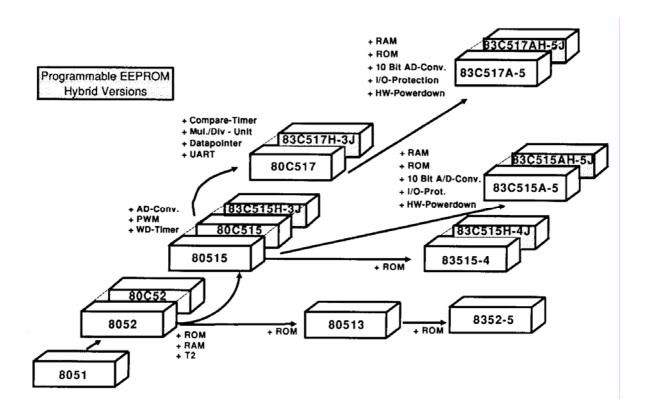

Aufbauend auf denn 8051, der von Intel entwickelt wurde, wurden zahlreiche Derivate von verschiedenen Firmen entwickelt. Als Vertreter solcher Derivate seien der Microcontroller 83C552 von Philips und der 80C517 von Siemens genannt. Beide sind leistungsfähige Erweiterungen des 8051. Sie enthalten den kompletten 8051, besitzen eine Menge von zusätzlichen Peripheriefunktionen und sind völlig softwarekompatibel.

Überblick der 8051-Familie von Ciemens

### 2.1 Die Architektur des MAB 8051 AH

#### 2.1.1 Überblick

### Die wesentlichen Merkmale des Mikrocontrollers MAB 8051 AH sind:

- 8bit-Zentraleinheit (CPU),

- 4KByte-Programmspeicher (ROM),

- 128Byte-Datenspeicher (RAM),

- 21 spezielle Funktionsregister,

- 32 E/A-Leitungen,

- 64KByte-Adressierbereich für den externen Datenspeicher,

- 64KByte-Adressierbereich für den Programmspeicher (extern u. intern zusammen),

- zwei 16bit-Zeitgeber/Zähler,

- Interrupts aus 5 Quellen mit 2 Prioritäten,

- serieller Port (Vollduplex),

- Boolescher Prozessor,

- Oszillator- und Taktgeberschaltungen (auf dem Chip),

- Multiplikation und Division durch je einen Befehl möglich,

- nicht pageorientierter Programmspeicher.

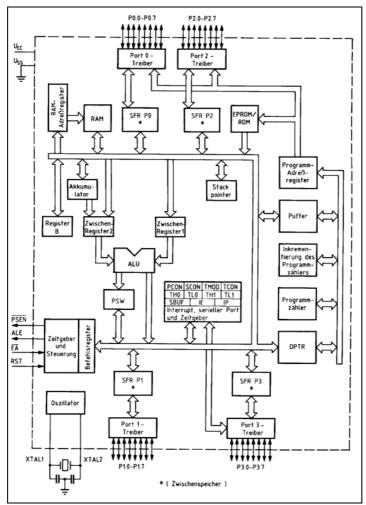

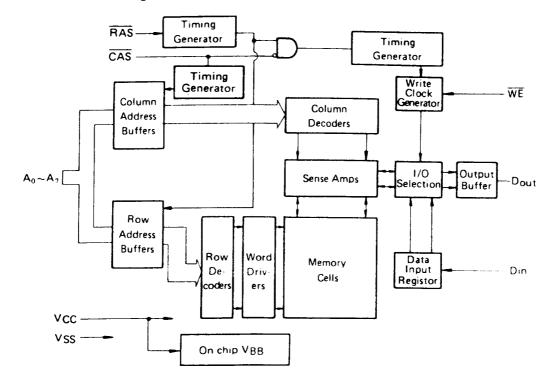

Abb. Blockschaltung des MAB 8051 AH.

#### 2.1.2 Speicheraufbau

Der MAB 8051 AH und der MAB 8031 AH verfügen über getrennte Adressierbereiche für den Programmspeicher und den Datenspeicher. Der externe Programmspeicher kann bis zu 64 KBytes umfassen; außerdem befinden sich im ROM auf dem Chip des MAB 8051 AH weitere 4 KBytes. Der Datenspeicher besteht aus einem auf dem Chip befindlichen RAM von 128 Bytes. In einem weiteren Adressierbereich von 128 Bytes sind nur 21 Bytes mit speziellen Funktionsregistern belegt. Außerdem kann die Schaltung auf bis zu 64 KBytes eines externen Datenspeichers zugreifen.

In der vorrigen Abbildung sind die 21 speziellen Funktionsregister mit ihren Kurzbezeichnungen sowie Speicherplätzen aufgeführt und anschließend kurz beschrieben. Die mit einem Stern versehenen Register sind sowohl byte- als auch bitadressierbar (11 Register mit Adressen, die durch 8 ohne Rest teilbar sind).

#### 2.1.3 Akkumulator

Das Register ACC ist der Akkumulator. In den mnemonischen Kurzbezeichnungen, die für Befehle mit Bezug auf den Akkumulator verwendet werden, wird der Akkumulator nur mit A bezeichnet.

### 2.1.4 Register B

Das Register B wird beim Multiplizieren und Dividieren benötigt. Bei der Abarbeitung anderer Befehle kann es als weiterer schneller Hilfsspeicher dienen.

| Tabelle: Spezielle Funktionsregister des MAB 8051 AF | Tabelle: | Spezielle | <b>Funktion</b> : | sregister des | MAB | 8051 AH |

|------------------------------------------------------|----------|-----------|-------------------|---------------|-----|---------|

|------------------------------------------------------|----------|-----------|-------------------|---------------|-----|---------|

| Kurzbezeichnung |                                       | Register | Adresse |

|-----------------|---------------------------------------|----------|---------|

| für Assembler   |                                       |          | hexa-   |

|                 |                                       | dezimal  | dezimal |

| ACC*)           | Akkumulator                           | 224      | EO      |

| B*)             | Register B                            | 240      | FO      |

| PSW*)           | Programmstatuswort                    | 208      | DO      |

| SP              | Stack pointer                         | 129      | 81      |

| DPH             | Datenzeiger (DPTR) oberes Byte        | 131      | 83      |

| DPL             | Datenzeiger (DPTR) unteres Byte       | 130      | 82      |

| PO*)            | Port 0                                | 128      | 80      |

| Pl *)           | Port 1                                | 144      | 90      |

| P2*)            | Port 2                                | 160      | AO      |

| P3*)            | Port 3                                | 176      | BO      |

| IP*)            | Interrupt-Prioritäten-Register        | 184      | B8      |

| IE*)            | Interrupt-Freigabe-Register           | 168      | A8      |

| TMOD            | Zeitgeber/Zähler-Betriebsart-Register | 137      | 89      |

| TCON*)          | Zeitgeber/Zähler-Steuerregister       | 136      | 88      |

| THO             | Zeitgeber/Zähler 0 (oberes Byte)      | 140      | 8C      |

| TLO             | Zeitgeber/Zähler 0 (unteres Byte)     | 138      | 8A      |

| TH1             | Zeitgeber/Zähler 1 (oberes Byte)      | 141      | 80      |

| TL1             | Zeitgeber/Zähler 1 (unteres Byte)     | 139      | 8B      |

| SCHON*)         | serielles Steuerregister              | 152      | 98      |

| SBUF            | serieller Datenpuffer                 | 153      | 99      |

| PCON            | Energie-Steuerregister                | 135      | 87      |

| ψ\ 11', 1 ' '   | 1                                     |          |         |

\*) auch bitadressierbar

### 2.1.5 Programmstatusregister

Das Programmstatusregister (PSW) enthält das in der nachstehenden näher beschriebene Programmstatuswort.

### 2.1.6 Stack pointer

Der 8 bit breite Stack pointer (SP) wird inkrementiert, bevor Daten während der Ausführung eines PUSH- oder CALL-Befehls gespeichert werden. Während der Stack im allgemeinen irgendwo im RAM (auf dem Chip) untergebracht sein kann, zeigt der Stack pointer nach einem Rücksetz-Vorgang auf den Speicherplatz 07H. Dies veranlaßt den Stack, mit Speicherplatz 08H zu starten.

#### 2.1.7 Datenzeiger

Der 16bit-Datenzeiger (DPTR) besteht aus den Registern DPH (oberes Byte) und DPL (unteres Byte). Er enthält eine 16bit-Adresse und kann entweder als 16bit-Register oder als zwei unabhängige 8bit-Register arbeiten.

#### 2.1.8 Ports 0 bis 3

Die speziellen Funktionsregister PO, Pl, P2 und P3 sind die Zwischenspeicher für die Ports PO, Pl. P2 bzw. P3.

#### **Programmstatusregister**

|           |                                            |        | $\overline{}$ | $\overline{}$                                                                                                |                                                                                                            |                |             |            |            |

|-----------|--------------------------------------------|--------|---------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------|-------------|------------|------------|

| CY        |                                            | AC F   |               |                                                                                                              | RS1                                                                                                        | RS0            | ov          |            | Р          |

| Symbol    | mbol Bit-Speicherstelle Name und Bedeutung |        |               |                                                                                                              |                                                                                                            |                |             |            |            |

| CY        |                                            | PSW.7  | 7             | Üb                                                                                                           | ertragsbit                                                                                                 |                |             |            |            |

| AC        |                                            | PSW.5  |               | Hil                                                                                                          | fsübertrag                                                                                                 | sbit (für BC   | D-Operation | nen)       |            |

| F0        | l                                          |        |               | ı                                                                                                            | _                                                                                                          |                |             |            | allgemeine |

|           |                                            |        |               | Zw                                                                                                           | ecke zur V                                                                                                 | erfügung)      |             |            |            |

| RS1       |                                            | PSW 4  | PSW.4         |                                                                                                              | Registerbank-Auswahlbits 1 bzw. 0. Werden durch Software gesetzt oder gelöscht, um die Registerbank auszu- |                |             |            |            |

| RS0       |                                            | PSW.3  |               |                                                                                                              |                                                                                                            |                |             |            |            |

|           | 1                                          |        |               | wählen, in der gearbeitet werden soll.*)                                                                     |                                                                                                            |                |             |            |            |

| OV        |                                            | PSW.2  | -             | Überlaufbit                                                                                                  |                                                                                                            |                |             |            |            |

| —<br>Р    |                                            | PSW.1  |               | in Reserve                                                                                                   |                                                                                                            |                |             |            |            |

| Р         |                                            | PSW.0  |               | Paritätsbit. Wird durch Hardware bei jedem Befehlszyklus gesetzt bzw. gelöscht, um eine ungerade bzw. gerade |                                                                                                            |                |             |            |            |

|           |                                            |        |               |                                                                                                              |                                                                                                            |                |             |            |            |

|           |                                            |        |               |                                                                                                              |                                                                                                            | insen im Al    | kkumulator  | anzuzeigen | 1          |

|           | L                                          |        |               | (d.                                                                                                          | h. gerade                                                                                                  | Pantat).       |             |            |            |

| ) Durch R | S1 unc                                     | RS0 wi | rd diese      | Regis                                                                                                        | terbank wie                                                                                                | e folgt festge | elegt:      |            |            |

| RS1       | RS0                                        | Bank   | Speicl        | nerplät                                                                                                      | ze                                                                                                         |                |             |            |            |

| 0         | 0                                          | 0      | 00H-07H       |                                                                                                              |                                                                                                            |                |             |            |            |

| 0         | 1                                          | 1      | 08H-0FH       |                                                                                                              |                                                                                                            |                |             |            |            |

| 1         | 0                                          | 2      | 10H-17H       |                                                                                                              |                                                                                                            |                |             |            |            |

|           | 1                                          | 1 2 1  | 100           | —1FH                                                                                                         |                                                                                                            |                |             |            |            |

#### 2.1.9 Zeitgeber-Register

Die Registerpaare THO und TLO sowie TH1 und TL1 sind 16bit-Zählregister für die Zeitgeber/Zähler 0 bzw. 1.

#### 2.1.10 Serieller Datenpuffer

Der serielle Datenpufter (SBUF) besteht eigentlich aus zwei separaten Registern, nämlich einem Sendepuffer- und einem Empfangspufferregister. Wenn Daten nach SBUF transportiert werden, so erfolgt dies in das Sendepufferregister; der Transport eines Bytes nach SBUF löst dann die Übertragung in eine externe Einheit aus. Werden Daten von SBUF geholt (von einer Einheit auf dem Chip), so kommen sie aus dem Empfangspufferregister.

### 2.1.11 Steuerregister

Die speziellen Funktionsregister IP, IE, TMOD, TCON, SCON und PCON enthalten Steuer- und Statusbits für das Interruptsystem, die Zeitgeber/Zähler und den seriellen Port. Sie werden in späteren Abschnitten beschrieben.

| - | ١. |   | 4  | • |    |   |   |

|---|----|---|----|---|----|---|---|

| Г | N  | Λ | Ť١ | 7 | Δ١ | n | • |

|   |    |   |    |   |    |   |   |

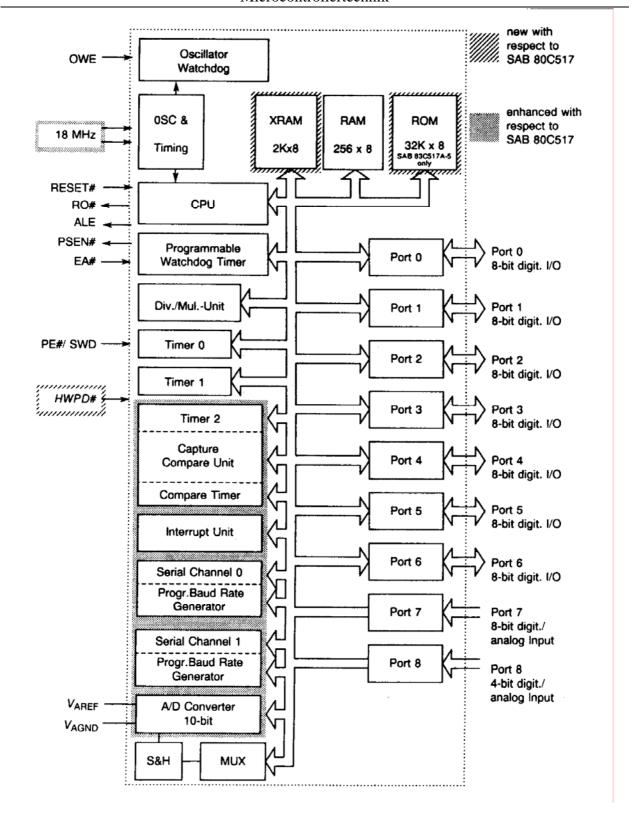

### 3 Überblick über den 80C517/80C517A

- **➣** 8 Kbyte On-Chip-ROM beim 80C517

- ≥ 32 Kbyte On-Chip-ROM beim 83C517A-5

- ➤ ROM-lose Varianten sind auch erhältlich (80C537 und 80C517A)

- ➤ Aufwärtskompatibel zum 8051 und 80515

- ≥ 256 Byte On-Chip-RAM

- ➤ Zusätzliche 2 Kbyte On-Chip-RAM beim 80C517A

- **⋈** Einzelbitverarbeitung

- > Versionen mit verschiedenen Taktgeschwindigkeiten erhältlich

- Externe Erweiterbarkeit von Programm- und Datenspeicher (je 64 Kbyte)

- Son-Chip-A/D-Wandler (8 bit- Version beim 80C517, 10 bit- Version beim 80C517A) 12 Eingänge, wahlweise interner oder externer Start.

- ≥ Zwei 16-bit Timer, voll kompatibel zum 80(C)51.

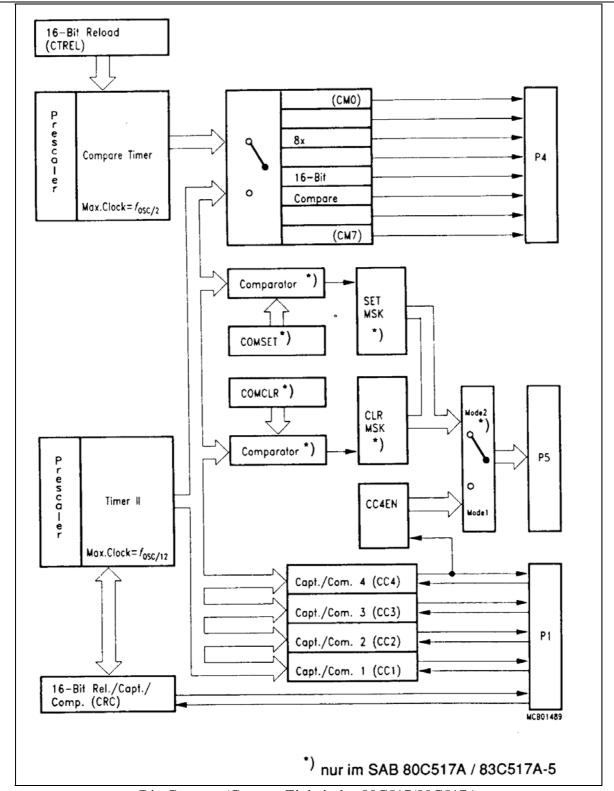

- ☑ Universelle Compare/Capture-Einheit mit eigenen 16-bit Timern; unterschiedlich konfigurierbare 16-bit-Compare- und Capture-Register für zeitliche Auflösungen.

- Arithmetik-Einheit für 16-bit-Arithmetik (Multiplikation, Division, Schiebeoperationen)

- ➤ Integrierte Systemüberwachung: Programmierbarer 16-bit-Watchdog-Timer, Oszillator-Watchdog.

- Neun Eingabe-Ausgabe-Ports, unterschiedlich konfigurierbar

- 🖾 Zwei unabhängige serielle Schnittstellen mit eigener Baudratenerzeugung

- ➤ Interrupt-System mit 14 (beim 80C517) bzw. 17 (beim 80C517A) Interrupt-Vektoren und 4 Prioritätsebenen.

- Betriebsarten zur Reduzierung der Stromaufnahme:

- Slow-Down-Modus Idle- Modus Power-Down-Modus

- □ Gefertigt in CMOS-Technologie

- ☑ Unterschiedliche Gehäusevarianten erhältlich: PLCC84, PQFP 100

Funktionsdiagramm des 80C517/80C517A

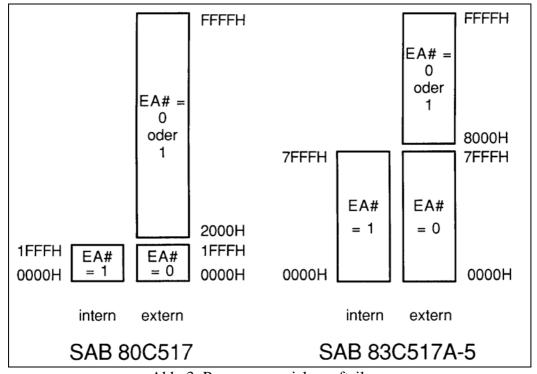

# 3.1 Speicherorganisation

### 3.1.1 Allgemeines

Der Speicherraum ist logisch und physikalisch in vier verschiedene Bereiche unterteilt.

- a) bis zu 64 Kbyte Programmspeicher adressierbar.

- b) bis zu 64 Kbyte externer Datenspeicher adressierbar.

- c) 256 Byte interner Datenspeicher

- d) ein 128 Byte großer Bereich für Special-Function-Register (SFR)

Abb. 3: Programmspeicheraufteilung

Im Bereich von 03H bis 93H liegen beim 80C517 des Programmspeichers die Einsprungadressen für die Interrupt-Routinen. Wenn einzelne Interrupts nicht benutzt werden, können aber diese Bereiche selbstverständlich für normalen Code verwendet werden.

#### 3.1.2 Interner Datenspeicher

| Speicherbereich     | Adresse      | Adressierungsart |

|---------------------|--------------|------------------|

| Untere 128 Byte RAM | 00H bis 7FH  | direkt/indirekt  |

| Obere 128 Byte RAM  | 80H bis 0FFH | indirekt         |

| SFR                 | 80H bis 0FFH | direkt           |

Bulme Graz

Aufteilung des internen Datenspeichers

#### 3.1.3 Die Code-Data-Struktur des 8051

Alle Microcontroller der Familie 8051 verfügen über getrennte Adressierbereiche für den Programmspeicher und den Datenspeicher. Der externe Programmspeicher und der externe Datenspeicher kann bis zu 64 kByte umfassen.

Der Zugriff auf den exteren Programmspeicher wird über das Signal PSEN gesteuert. Für den Zugriff auf den Datenspeicher stehen die Signale RD und WR zur Verfügung. Die Struktur eines solchen Speichersystems wird Harvard Struktur genannt.

Harvard Struktur

Bulme Graz

Die Harvard Struktur wird während des normalen Betriebs des Mikrocontrollers verwendet. Zur Programmentwicklung wird jedoch eine andere Speicherstruktur verwendet. Sie wird Neumann Struktur genannt. Bei der Neumann Struktur liegt der Datenspeicher und der Programmspeicher in einem gemeinsamen Adressbereich. Dazu muß das Signal RD, welches aus dem RAM liest, und das Signal PSEN, welches aus dem ROM liest, verknüpft werden. Die UND Verknüpfung der beiden Signale ergibt ein Lesesignal für den gesamten Speicher.

Nötig ist diese Zusammenschaltung aus folgendem Grund: Während der Programmentwicklung läuft im ROM ein Monitorprogramm. Dieses kommuniziert über die serielle Schnittstelle mit dem PC. Auf dem PC wird das Anwenderprogramm geschrieben, compiliert, gelinkt und in ein INTEL Hex Format gebracht. Das Anwenderprogramm wird mit Hilfe des Monitors in das RAM des 8051 geladen und vom Monitorprogramm gestartet. Das Programm kann bequem getestet und auf Fehlfunktionen überprüft werden.

Erst wenn das Programm einwandfrei funktioniert, wird es in ein EPROM gebrannt. Dann wird wieder die Harvard Stuktur mit getrenntem Code- und Datenbereich verwendet.

### 4 C-Programme für den 8051

### 4.1 Allgemeines

Zur Programmierung der Mikrocontroller der Familie 8051 steht ein C-Compiler der Firma Keil zur Verfügung.

Der Ablauf bei der Erstellung eines C-Programms sieht folgendermaßen aus:

Mit dem Texteditor wird der C Source Code eingegeben und mit dem C Compiler übersetzt. Dieser liefert einen absoluten Oject Modul für das Anlaufen des Programms an der Adresse 0 und einige verschiebbare (relocatable) Programm Module, denen erst beim Link Vorgang absolute Adressen zugewiesen werden. Beim Link Vorgang werden dann auch die mit dem C Compiler mitgelieferten Library Module, die von den Funktionsaufrufen angesprochen werden, in den Maschinencode miteingebunden.

Der Linker liefert den lauffähigen Code, der für die Datenübertragung mittels des Monitorprogramms noch mit einem Object Hex Konvertierungsprogramm in ASCII umgewandelt wird.

# 4.2 Zugriff auf Special Function Register

Für ein Beispielprogramm sollen die acht Leuchtdioden auf der Zusatzplatine blinken Die Leuchtdioden sind über einen Treiber an den Port 1 des 8051 angeschlossen. Das Programm muß folgende Aufgaben erfüllen:

Zuerst soll der Port 1 rückgesetzt werden, so daß keine LED leuchtet. Anschließend soll ein bestimmtes Bitmuster am Port 1 ausgegeben werden. Das Bitmuster soll abwechselnd **01010101** und **10101010** lauten, dies entspricht den beiden HexZahlen 0x55 und 0xAA.

Die im Hauptprogramm verwendete Bezeichnung P1 bezeichnet den Port 1 des Microcontrollers. Die zugehörige Datendefinition ist in der Datei REG517.H abgespeichert und lautet  $sfr\ P1 = 0x90$ . Die Abkürzung sfr steht für  $special\ function\ register$  und bezeichnet einen Datenypen zum Zugriff auf ein special function register des 8051. Die Zeile  $sfr\ P1 = 0x90$  sagt aus , daß das special function register, über welches man auf Port 1 zugreifen kann, im Programm P1 heißt und intern im Speicher des 8051 die Adresse  $90Hex\ (0x90)$  hat.

Bulme Graz

Der C Source Code wird mit dem Texteditor von MS DOS eingegeben. Dieser wird mit dem Befehl *C:*\>*edit* gestartet.

```

/*

PORT.C

* /

/*

* /

Erstes Testprogramm für BULME - Graz

Steueranweisungen an den Compiler

****/

#pragma noiv

#pragma mod517

#pragma code debug pl(61)

****/

Angabe der Include Dateien

#include <reg517.h>

Prototypen der Funktionen

****/

void warte(unsigned int msec);

/****

Funktionen

****/

void warte(unsigned int msec)

{ data char i;

for (msec; msec!=0; msec--) for (i=0; i<83; i++);

Hauptprogramm

main()

{

P1 = 0x00;

warte (1000);

P1 = 0xAA;

warte (1000);

P1 = 0x55;

warte (1000);

P1 = 0xAA;

warte (1000);

P1 = 0x00;

}

```

Der eingegebene Code wird unter dem Namen **PORT.C** abgespeichert und der Editor beendet.

Die Compilierung des C-Source Codes erfolgt mit dem Aufruf:

C51 PORT.C

# 5 Standardbeschaltung des Microcontrollers 80C537

Bulme Graz Seite 20

# 6 Serielle Schnittstelle(n)

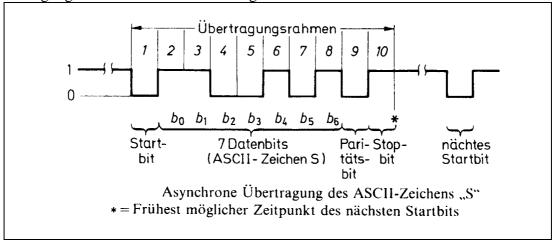

Die RS232E-Schnittstelle dient zur asynchronen seriellen Punkt zu Punkt Datenübertragung. Ein Startbit eröffnet den Übertragungsrahmen eines Zeichens. Darauf folgen die 7 Bit des ASCII-Kodes, oder die 8 Bit bei erweitertem Zeichenvorrat, gefolgt von einem Paritäts- und einem Stopbit, welches den Übertragungsrahmen abschließt.

Ein Übertragungsrahmen sieht dabei wie folgt aus:

Das Startbit löst im Empfänger einen zeitlichen Ablauf aus, der die einzelnen Elemente des gesendeten Kodes indiziert. Daher muß der Empfänger über die zeitliche Dauer der Elemente a priori informiert sein.

Als Erinnerung an den Fernschreiber ist der Ruhezustand des Schnittstellensignals die logische Eins. Der Linienstrom läßt erkennen, ob die Fernschreibleitung unterbrochen ist.

Das Paritätsbit dient der Fehlererkennung. Der Wert des Paritätsbits wird von der Zahl der Einsen im Datenwort bestimmt. Er ist 0 wenn bei gerader (even) Parität die Zahl der Einsen gerade ist oder bei ungerader (odd) Parität ungerade ist. Die gerade Parität kann daher auch als modulo 2-Summe der Datenbits erhalten werden.

Der Übertragungsrahmen (Frame) wird durch ein, im Sonderfall zwei, Stopbits abgeschlossen.

Die Übertragungsgeschwindigkeit wird in Baud angegeben. Ein Baud entspricht einer Rate von 1 bit/s (bps). Die Übertragungsgeschwindigkeiten sind genormt. Sie müssen beim Sender und Empfänger gleich eingestellt werden. Gängige Übertragungsgeschwindigkeiten sind 75, 150, 300, 600, 1200, 2400, 4800, 9600, 19200 baud.

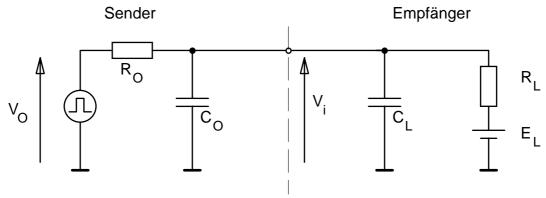

#### Elektrische Eigenschaften der asynchronen seriellen Schnittstelle RS232E:

Die elektrischen Eigenschaften der Spannungsschnittstelle (CCITT-Empfehlung<sup>1</sup> V.24; EIA/TIA-Standard<sup>2</sup> RS232E (1990); DIN 66020) gültig für Datenraten < 20000 baud werden

<sup>&</sup>lt;sup>1</sup> CCITT International Telegraph and Telephone Consulative Committee

<sup>&</sup>lt;sup>2</sup> EIA Electronics Industries Association

TIA Telecomunications Industry Association

anhand des Ersatzschaltbildes einer Zweidrahtschnittstelle (ohne Potentialtrennung) beschrieben.

Ersatzschaltung für die RS232E Schnittstelle nach EIA-Standard

Die Leerlaufspannung des Senders  $V_O$  soll kleiner als 25 V sein. Der Innenwiderstand des Senders  $R_O$  soll so bemessen sein, daß bei Kurzschluß in der Übertragungsleitung (auch zu benachbarten Adern) der Strom auf 0,5 A begrenzt wird. Im ausgeschalteten Zustand des Senders soll die Schnittstellenspannungen kleiner 2 V und  $R_O > 300$  W sein. Daher ist in manchen Senderschaltungen ein ohmscher Widerstand dieser Größe zur Strombegrenzung vorgesehen.

Die Ausgangskapazität  $C_0$  wird meist mit der Lastkapazität für den Sender  $C_L$  (Eigenkapazität des Empfängers und Kapazität der Leitung) gemeinsam betrachtet. Die Gesamtkapazität soll dabei nicht größer als 2500 pF sein. Dadurch wird die Länge der Leitung auf etwa 10 m begrenzt.

Der Lastwiderstand  $R_L$  (Eingangswiderstand des Empfängers) muß zwischen 3 und 7 kW liegen. Eine eventuelle innere Spannung des Empfängers (meist Basisemitterspannungen) < 2 V sein.

Im Normalbetrieb ( $E_L$ =0) muß  $V_O$  so bemessen sein, daß die Schnittstellenspannung  $V_i$  zwischen 5 und 15 V beträgt. Positive Werte für die logische Null, negative für die logische Eins. Das bedeutet implizit, daß dür den Sender zwei Betriebsspannungen deutlich größer als  $\pm$  5 V notwendig sind. Die Verwendung der TTL Versorgungsspannungen als Betriebsspannung für die Schnittstelle stellt nur eine Behelfslösung dar.

Der Empfänger soll Spannungen zwischen 3 und 25 V entsprechend dem Vorzeichen richtig erkennen können. Der Übergangsbereich zwischen -3 und +3 V dient zur Erkennung eines Senderausfalles oder einer Leitungsunterbrechnung. Gute Empfängerbausteine signalisieren diesen Zustand getrennt vom Datenausgang. Das Schnittstellensignal soll den Übergangsbereich von einem Signalzustand zum anderen durchqueren, dabei seine Richtung nicht ändern und erst nach der nächsten Änderung des logischen Zustandes wieder in den Übergangsbereich eintreten. Die Zeit für das Passieren des Übergangsbereiches soll < 1 ms sein, zusätzlich auch < 4 % der Dauer eines Signalelementes bei Daten- und Taktsignalen. Die Zeitliche Änderung der Schnittstellenspannung muß immer < 30 V/ms sein (Schwarzsender?).

Bulme Graz

Beispiel für einen Schnittstellenbaustein für die wechselweise Pegelumsetzung zwischen 5 V CMOS- (auch TTL-) und RS232-Pegeln. Der eingebaute Spannungswandler erzeugt die Betriebsspannungen für die Schnittstellentreiber intern nach dem Prinzip der Ladungspumpe aus der 5 V Versorgung.

## 6.1 RS232-Schnittstelle an einem Personal Computer:

Bei der heute gängigen Schnittstelle zur Verbindung eines Personalcomputers mit einem beliebigen peripheren Gerät.

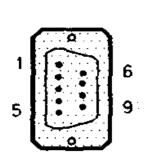

9-poliger Stecker

Steckerbelegung an einem Personalcomputer

| 9-pol. | 25-pol. | Abk. | Bedeutung           |         |

|--------|---------|------|---------------------|---------|

| 1      | 8       | DCD  | Carrier Detect      | Ausgang |

| 2      | 3       | RxD  | Received Data       | Eingang |

| 3      | 2       | TxD  | Transmitted Data    | Ausgang |

| 4      | 20      | DTR  | Data Terminal Ready | Eingang |

| 5      | 7       | GND  | Signal Ground       |         |

| 6      | 6       | DSR  | Data Set Ready      | Ausgang |

| 7      | 4       | RTS  | Request to Send     | Ausgang |

| 8      | 5       | CTS  | Clear to Send       | Eingang |

| 9      | 22      | RI   | Ring Indicator      | Eingang |

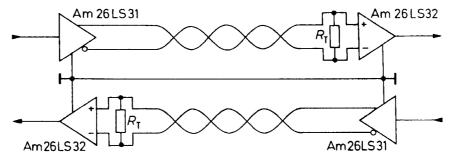

#### **6.2** Andere serielle Schnittstellen:

### **RS423 (V.10 in Europa):**

Diese Schnittstelle hat einen kleineren Spannungshub (swing).

Schaltschwellen:

Sender: +/- 3,6 Volt

Empfänger: +/- 0,2 Volt

Sie ist eine unsymmetrische Schnittstelle. Die Massen müssen nicht miteinander verbunden werden. Die RS423 stellt eine echte Punkt-zu-Punkt-Verbindung (wegen Koaxkabel) dar. Die Leitung muß mit dem Wellenwiderstand abgeschlossen sein. Die maximale Datenrate beträgt 300 kbaud bei 30m Leitungslänge und reduziert sich bis auf 15 kbaud bei 600m Leitungslänge.

Anordnung einer RS 423-Schnittstelle

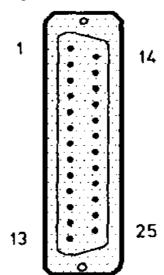

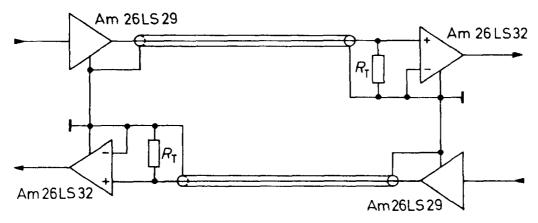

#### **RS422 (V.11 in Europa):**

Schaltschwellen:

Sender: +/- 3,6 Volt Empfänger: +/- 0,2 Volt

Anordnung einer RS 422-Schnittstelle

Leitung: verdrilltes Leitungspaar mit einer maximalen Länge von 1200m

Bulme Graz Seite 24

Zwei Eintakttreiber werden im Gegentakt angesteuert. Die Ausgangsspannungen sind zueinander komplementär. Gleichtaktstörungen werden dadurch "wegsubtrahiert". Übertragungsraten von maximal 2Mbaud bei einer maximalen Leitungslänge von 60m sind erreichbar. Bei größeren Leitungslängen reduziert sich die Datenrate bis auf 100kbaud.

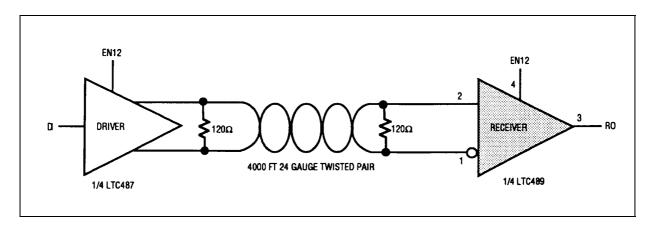

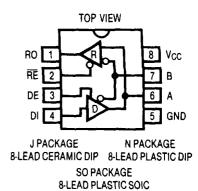

#### **RS485:**

| Supply Voltage (V <sub>CC</sub> )12V                     | 1 |

|----------------------------------------------------------|---|

| Control Input Voltages 0.5V to V <sub>CC</sub> + 0.5V    |   |

| Driver Input Voltage – 0.5V to V <sub>CC</sub> + 0.5V    | , |

| Driver Output Voltages ± 14V                             | 1 |

| Receiver Input Voltages ± 14V                            | , |

| Receiver Output Voltage – 0.5V to V <sub>CC</sub> + 0.5V | 1 |

| Operating Temperature Range                              |   |

| LTC485I 40°C≤T <sub>A</sub> ≤85°C                        | ; |

| LTC485C0°C≤TA≤70°C                                       | ; |

# 6.3 Die seriellen Schnittstellen des 80C517

### 6.3.1 Serielle Schnittstelle 0

Die serielle Schnittstelle 0 arbeitet in vier Betriebsarten. Das dazugehörige Steuerregister ist S0CON.

#### S0CON (98H), bitadressierbar

| MSB |     |      |      |      |      |     | LSB |

|-----|-----|------|------|------|------|-----|-----|

| SM0 | SM1 | SM20 | REN0 | TB80 | RB80 | TI0 | RI0 |

| 9FH | 9EH | 9DH  | 9CH  | 9BH  | 9AH  | 99H | 98H |

Steuerregister der seriellen Schnittstelle 0 (Serial Interface 0 Control). Es enthält Steuerbits für die serielle Schnittstelle 0.

Reset-Wert: 00H

| Bitsymbol |     | Funktion                                                                                                                                                                                                                                                                                         |

|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SM0       | SM1 | Serieller Modus Bit 0/1                                                                                                                                                                                                                                                                          |

| 0         | 0   | Modus 0: Schieberegister-Modus                                                                                                                                                                                                                                                                   |

| 0         | 1   | Modus 1: 8-Bit-UART, flexible Baudrate                                                                                                                                                                                                                                                           |

| 1         | 0   | Modus 2: 9-Bit-UART, feste Baudrate                                                                                                                                                                                                                                                              |

| 1         | 1   | Modus 3: 9-Bit-UART, flexible Baudrate                                                                                                                                                                                                                                                           |

| SM        | 120 | Aktiviert den Multiprozessor-Kommunikationsbetrieb in Modus 2 und 3. Mit SM20 = 1 in Modus 2 und 3 wird RIO nicht gesetzt, wenn das 9. empfangene Datenbit 0 ist. Mit SM20 = 1 in Modus 1 wird RIO nicht gesetzt, wenn kein gültiges Stoppbit empfangen wurde. In Modus 0 muß SM20 immer 0 sein. |

| RE        | N0  | Empfängeraktivierung (Receive Enable). wenn REN0 auf 1 gesetzt ist, ist serieller Empfang möglich, mit REN0 = 0 ist serieller Empfang abgeschaltet. Muß durch Software gesetzt/rückgesetzt werden.                                                                                               |

| ТВ        | 80  | Sendebit 8 (Transmitter Bit 8). Dies ist das 9. Datenbit, das in Modus 2 und 3 ausgesendet wird. Muß durch Software gesetzt/rückgesetzt werden.                                                                                                                                                  |

| RB80      |     | Empfangsbit 8 (Receiver Bit 8). Dies ist das 9. Datenbit, das in Modus 2 und 3 empfangen wird. In Modus 1 (mit SM20 = 0) ist RB80 das empfangene Stoppbit. In Modus 0 wird RB80 nicht benutzt.                                                                                                   |

| TIO       |     | Sende-Interrupt (Transmitter Interrupt). Dies ist das Interrupt-Request-Flag für den Sender. TIO wird von derH ardware in Modus 0 am Ende des 8. Datenbits gesetzt, in den anderen Modi bei Beginn des Stoppbits. TIO muß durch Software rückgesetzt werden.                                     |

| RI0       |     | Empfänger-Interrupt (Receiver Interrupt). Dies ist das Interrupt-Request-Flag für den Empfänger. RIO wird in Modus 0 von der Hardware am Ende des 8. Datenbits gesetzt, in den anderen Modi während des Stoppbits. RIO muß durch Software rückgesetzt werden.                                    |

Bild 8-2: Special-Function-Register S0CON (98H)

### PCON (87H), nicht bitadressierbar

| MSB  |     |      |    |     |     |     | LSB  |

|------|-----|------|----|-----|-----|-----|------|

| SMOD | PDS | IDLS | SD | GF1 | GF0 | PDE | IDLE |

|      |     |      |    |     |     |     |      |

Steuerregister für die Stromaufnahme (Power Control Register). Es enthält Steuerbits für die Stromaufnahme und die serielle Schnittstelle 0.

Reset-Wert: 00H

| Bitsymbol | Funktion                                                                   |

|-----------|----------------------------------------------------------------------------|

| SMOD      | Bei gesetztem Bit SMOD verdoppelt sich die Baudrate der seriellen Schnitt- |

|           | stelle 0 in den Modi 1,2 und 3                                             |

Bild 8-3: Special-Function-Register PCON (87H)

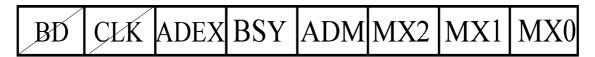

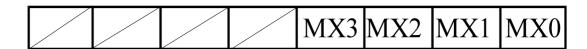

#### ADCON0 (D8H), bitadressierbar

| MSB |     |      |     |     |     |     | LSB |

|-----|-----|------|-----|-----|-----|-----|-----|

| BD  | CLH | ADEX | BSY | ADM | MX2 | MX1 | MX0 |

| DFH | DEH | DDH  | DCH | DBH | DAH | D9H | D8H |

A/D-Wandler-Steuerregister 0 (A/D Converter Control Register 0). Es enthält Steuerbits für den A/D-Wandler und die serielle Schnittstelle 0.

Reset-Wert: 00H.

| Bitsymbol | Funktion                                                                                                                                                                                                                                                                                                    |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BD        | Freigabebit für den Baudratengenerator der seriellen Schnittstelle 0. Wenn es gesetzt ist, wird die Baudrate in den Modi 1 und 3 vom Baudratengenerator der seriellen Schnittstelle 0 abgeleitet. Damit können die Standardbaudraten 4,8 KBaud bzw. 9,6 KBaud bei 12 MHz Oszillatorfrequenz erzeugt werden. |

Bild 8-4: Special-Function-Register ADCON0 (D8H)

In Bild 8-7 sind einige repräsentative Betriebsfälle bei Baudratenerzeugung mit Timer 1 herausgegriffen.

| Baudrate in<br>Modus 1 u. 3 | fosz [MHz] | SMOD |      | Timer 1 |        |

|-----------------------------|------------|------|------|---------|--------|

|                             |            |      | C/T# | Modus   | Reload |

| 62,5 KBaud                  | 12,000     | 1    | 0    | 2       | FFH    |

| 19,2 KBaud                  | 11,059     | 1    | 0    | 2       | FDH    |

| 9,6 KBaud                   | 11,059     | 0    | 0    | 2       | FDH    |

| 4,8 KBaud                   | 11,059     | 0    | 0    | 2       | FAH    |

| 2,4 KBaud                   | 11,059     | 0    | 0    | 2       | F4H    |

| 1,2 KBaud                   | 11,059     | 0    | 0    | 2       | E8H    |

| 110 Baud                    | 6,000      | 0    | 0    | 2       | 72H    |

| 110 Baud                    | 12,000     | 0    | 0    | 1       | FEEBH  |

Bild 8-7: Baudratenerzeugung mit Timer 1

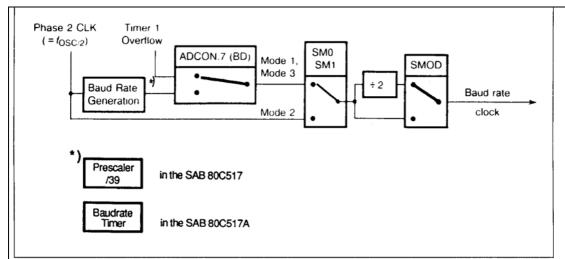

Bild 8-8: Baudratenerzeugung für die serielle Schnittstelle 0

| Baudratentakt<br>abgeleitet von     | Modus  | Baudrate                                                                                                                       |

|-------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------|

| Timer 1 in Modus 1 (siehe Bild 7-7) | 1 u. 3 | $\frac{2^{\text{SMOD}}}{2} * \frac{1}{16} * \text{ (Timer 1-Überlaufrate)}$                                                    |

| Timer 1 in Modus 2                  | 1 u. 3 | $\frac{2^{\text{SMOD}}}{2} * \frac{1}{16} * \frac{f_{\text{osz}}}{12 * (256 - (\text{TH1}))}$                                  |

| Oszillator                          | 2      | $\frac{2^{\text{SMOD}}}{2} \star \frac{1}{16} \star \frac{f_{\text{osz}}}{2}$                                                  |

| Baudratengenerator im 80C517        | 1 u. 3 | $\frac{2^{\text{SMOD}}}{2} * \frac{f_{\text{osz}}}{1250}$                                                                      |

| Baudratengenerator im 80C517A       | 1 u. 3 | $\frac{2^{\text{SMOD}}}{2} * \frac{1}{32} * \frac{f_{\text{osz}}}{2^{10} - \text{SOREL}}$ (mit SOREL = SORELH.1-0, SORELL.7-0) |

Bild 8-9: Formeln für Baudraten für die serielle Schnittstelle 0

#### 6.3.2 Serielle Schnittstelle 1

Die serielle Schnittstelle 1 hat lediglich asynchrone Betriebsarten und kann ähnlich wie die serielle Schnittstelle 0 in den Modi 8- oder 9-bit-Datenübertragung arbeiten. Das dazugehörige SFR ist S1CON.

#### S1CON (9BH), nicht bitadressierbar

| MSB                                                                                                                                                       |                                |                                                                                                                                                                                                                                         |                              |              |      |                             | LSB |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------|------|-----------------------------|-----|

| SM                                                                                                                                                        | -                              | SM21                                                                                                                                                                                                                                    | REN1                         | TB81         | RB80 | TI1                         | RI1 |

| Steuerregister der seriellen Schnittstelle 1 (Serial Interface 1 Control). Es enthält Steuerbits für die serielle Schnittstelle 1. Reset-Wert: 0x00 0000B |                                |                                                                                                                                                                                                                                         |                              |              |      |                             |     |

| Bitsymbol                                                                                                                                                 | Funktio                        | n                                                                                                                                                                                                                                       |                              |              |      |                             |     |

| SM                                                                                                                                                        |                                |                                                                                                                                                                                                                                         | triebsart A;<br>triebsart B; |              |      |                             |     |

| SM21                                                                                                                                                      | Aktivier<br>= 1 wird<br>SM21 = | Aktiviert den Multiprozessor-Kommunikation-Betrieb in Modus A. Mit SM21 = 1 wird RI1 nicht gesetzt, wenn das 9. empfangene Datenbit 0 ist. Mit SM21 = 1 in Modus B wird RI1 nicht gesetzt, wenn kein gültiges Stoppbit empfangen wurde. |                              |              |      |                             |     |

| REN1                                                                                                                                                      | Empfan                         | Receive Enable; Enable für den Empfänger; wenn auf 1 gesetzt, ist serieller Empfang möglich, mit REN1 = 0 ist serieller Empfang abgeschaltet. Es muß durch Software gesetzt/rückgesetzt werden.                                         |                              |              |      |                             |     |

| TB81                                                                                                                                                      |                                | Transmitter Bit 8; Dies ist das 9. Datenbit, das in Modus A ausgesendet wird. Es muß durch Software gesetzt/rückgesetzt werden.                                                                                                         |                              |              |      |                             |     |

| RB81                                                                                                                                                      |                                | Receiver Bit 8; Dies ist das 9. Datenbit, das in Modus A empfangen wird. In Modus B (mit SM21 = 0) ist RB81 das empfangene Stoppbit.                                                                                                    |                              |              |      |                             |     |

| TI1                                                                                                                                                       | TI1 wire                       | Transmitter Interrupt; Dies ist das Interrupt-Request-Flag für den Sender. TI1 wird von der Hardware bei Beginn des Stoppbits gesetzt. TI1 muß durch Software rückgesetzt werden.                                                       |                              |              |      |                             |     |

| RI1                                                                                                                                                       | TI1 wire                       |                                                                                                                                                                                                                                         | les Stoppbit                 | s gesetzt. F |      | g für den En<br>ch Software |     |

Bild 8-10: Special-Function-Register S1CON (9BH)

### S1BUF (9CH), nicht bitadressierbar

MSB

S1BUF.7 S1BUF.6 S1BUF.5 S1BUF.4 S1BUF.3 S1BUF.2 S1BUF.1 S1BUF.0

Empfangs- und Sendepuffer der seriellen Schnittstelle 1 (Serial Interface 1 Buffer). Ein Schreibbefehl auf S1BUF lädt den Sendepuffer und startet eine Übertragung. Ein Lesebefehl auf S1BUF greift auf das physikalisch getrennte Empfangsregister zu. Reset-Wert: XXH

Bild 8-11: Special-Function-Register S1BUF (9CH)

#### Baudraten:

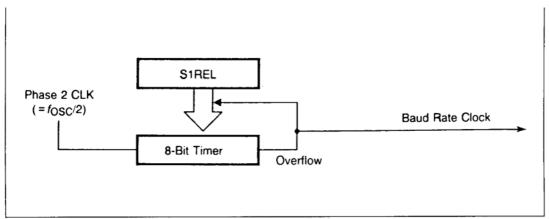

Bild 8-12: Baudratengenerator für serielle Schnittstelle 1 im 80C517

### S1REL (9DH), nicht bitadressierbar

| MSB     |         |         |         |         |         |         | LSB     |

|---------|---------|---------|---------|---------|---------|---------|---------|

| S1REL.7 | S1REL.6 | S1REL.5 | S1REL.4 | S1REL.3 | S1REL.2 | S1REL.1 | S1REL.0 |

Reload-Register (8 bit) für den Baudratengenerator der seriellen Schnittstelle 1 im 80C517. Nach Reset ist die Baudrate 1,5 KBaud bei 12 MHz Oszillatorfrequenz.

Reset-Wert: 00H

# 7 Speicher

### 7.1 Allgemeines

Halbleiter-Speicherschaltungen zum Schreiben und Lesen von Daten ("random access memory") lassen sich in zwei unterschiedliche Hauptgruppen einteilen. Dies sind der statische Schreib-Lese-Speicher, der eine FF-Struktur besitzt, und der dynamische Schreib-Lese-Speicher mit einem integrierten Speicherkondensator, dessen Ladung zyklisch aufgefrischt werden muß ("refresh").

Statische Schreib-Lese-Speicher, SRAM genannt ("static random access memory" = Speicher mit wahlfreiem Zugriff), weisen je nach Technologie zwei bis sechs Transistoren pro Speicherzelle auf. Bei der 6-Transistorzelle werden zwei Transistoren als Ersatz für die Lastwiderstände verwendet, weil Widerstände in integrierten Schaltungen einen großen Platzbedarf aufweisen. Der Begriff "Speicher mit wahlfreiem Zugriff" bedeutet, daß man auf jedes Wort zu jeder Zeit zugreifen kann, im Unterschied zum Schieberegisterspeicher (siehe später), bei dem die Daten nur in derselben Reihenfolge ausgelesen werden können, in der sie eingeschrieben wurden. Die Bedeutung von Schieberegisterspeicher ist in letzter Zeit gesunken. Deshalb ist der Begriff RAM zur generellen Bezeichnung für Schreib-Lese-Speicher geworden. Das ist insofern etwas irreführend, als die ROMs ebenfalls einen wahlfreien Zugriff auf jedes Datenwort haben.

Die dynamischen Schreib-Lese-Speicher (DRAM = "dynamic random access memory") benötigen zusätzlich zu den Speicherzellen aufwendige Hilfsschaltungen ("Refresh"-Verstärker und Ladungspumpen zur Erzeugung interner Hilfsspannungen), die einen nicht zu vernachlässigenden Flächenbedarf haben.

Ausgehend von gleicher Speicher-Bausteinfläche und Technologie liegt die Speicherkapazität bei DRAMs ca. um den Faktor vier höher als bei SRAMs.

ROM ist die Abkürzung des englischen Begriffs "Read Only Memory", d.h. Festwertspeicher. Damit werden Speicher ICs bezeichnet, die ihre Daten auch dann behalten, wenn sie ohne jede Versorgungsspannung, also auch ohne Hilfsbatterie, betrieben werden. Im Normalbetrieb werden sie nur gelesen. Die Speicherung der Daten erfordert in der Regel spezielle Geräte. Man bezeichnet den Speichervorgang in diesem Fall als Programmierung (siehe später).

# 7.2 Speicherorganisation:

Ein Speicherbaustein hat für seine interne Datenorganisation Anschlüsse für:

o Adresse (**n** für 2<sup>n</sup> Adressen (je nach Speichertiefe)

o Daten (1, 4, 8, 16 bit)

**SRAM-Beispiel:** SRM-20256LC-10 (32KBx8)

SRM-20... Firmenbezeichnung 256 ... 256 kbit Speichertiefe

LC ... CMOS

10 ... Zugriffszeit = 100ns

32 KByte ... Speichertiefe

Die Organisation für diesen Speicher ist 8 bit Datenbreite (Byte-Organisation) 8 bit Datenbreite = **BYTE**

16 bit Datenbreite = **WORD**

Dezimal ADRESSE DATENWORT

|         | 214             | 213             | 21                 | 20             | MSB            |                |                    | LSB   |

|---------|-----------------|-----------------|--------------------|----------------|----------------|----------------|--------------------|-------|

| Dezimal | A <sub>14</sub> | A <sub>13</sub> | <br>A <sub>1</sub> | A <sub>0</sub> | D <sub>7</sub> | D <sub>6</sub> | <br>D <sub>1</sub> | $D_0$ |

| 0       | 0               | 0               | 0                  | 0              |                |                |                    |       |

| 1       | 0               | 0               | 1                  | 0              |                |                |                    |       |

| 2       | 0               | 0               | 1                  | 1              |                |                |                    |       |

| 3       | 0               | 0               | 0                  | 0              |                |                |                    |       |

| •••     |                 |                 |                    |                |                |                |                    |       |

| •••     |                 |                 |                    |                |                |                |                    |       |

| •••     |                 |                 |                    |                |                |                |                    |       |

|         |                 |                 |                    |                |                |                |                    |       |

| 32765   | 1               | 1               | 0                  | 0              |                |                |                    |       |

| 32766   | 1               | 1               | 1                  | 0              |                |                |                    |       |

| 32767   | 1               | 1               | 1                  | 1              |                |                |                    |       |

Bulme Graz

#### 7.3 Statische RAMs:

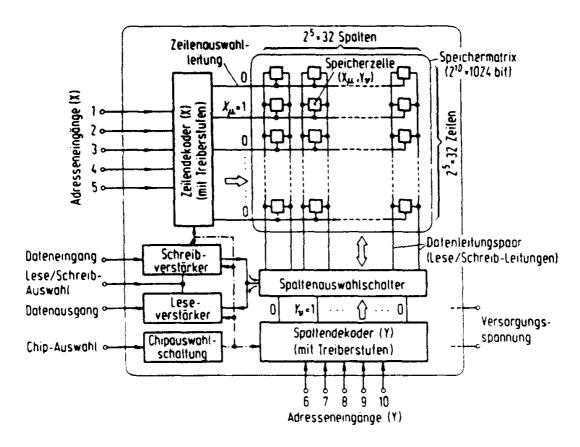

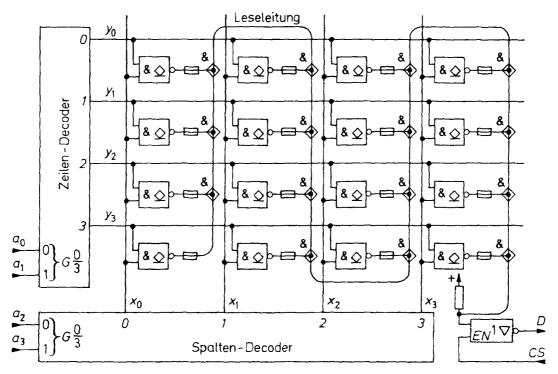

Ein RAM ist ein Speicher, bei dem man nach Vorgabe einer Adresse Daten abspeichern und unter dieser Adresse wieder auslesen kann (wahlfreier Zugriff). Aus technoilogischen Gründen werden die einzelnen Adressen nicht linear, sondern in einer quadratischen Matrix angeordnet. Zur Auswahl einer bestimmten Speicherstelle wird die Adresse A von einem Spalten- bzw. Zeilendecoder dekodiert.

Beispiel für eine Organisation eines 1024x1bit Speicherbausteins

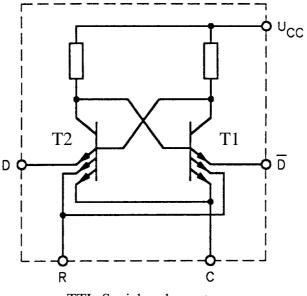

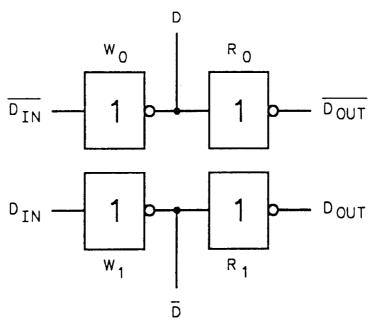

#### 7.3.1 TTL-Speicherzelle:

Die Auswahl jeder Speicherzelle erfolgt über die jeweilige Zeile (row) und der jeweiligen Spalte (column). Jeder Transistor (Multiemittertransistor) verfügt über eine weitere Emitterleitung ( $\overline{D}$  bzw. D), die alle mit entsprechenden Schreib- und Leseverstärkern verbunden sind. Über diese Leitungen werden Daten ein- oder ausgegeben. Die Adressierung des Speichers erfolgt durch die Dekodierung der Adressen A1 bis A10. Die Betriebsart (Schreiben oder Lesen) wird üblicherweise durch ein Steuersignal  $R/\overline{W}$  festgelegt. Beim Schreiben werden die Schreibverstärker W0 und W1 (siehe nächstes Bild) freigegeben und die Leseverstärker R0 und R1 gesperrt. Beim Lesen werden dann entsprechend die Leseverstärker freigegeben und die Schreibverstärker gesperrt.

TTL-Speicherelement

Die FF-Zelle wird angesprochen, wenn die Leitungen R und C hi-Pegel führen. Dadurch fließen die Emitterströme  $I_{EX}$  beim leitenden und  $I_{EY}$  beim gesperrten Transistor zu den angeschlossenen Leseverstärkern. Bei allen anderen FF-Zellen fließen die Emitterströme ausschließlich durch die Schalttransistoren der Dekoder ab.

Anordnung der Schreib/Lese-Verstärker bei statischen TTL-RAMs

Durch Aktivierung der Leseverstärker kann ein Datum  $D_{OUT}$  oder  $\overline{D_{OUT}}$  ausgegeben werden.

Für den Schreibvorgang werden die Schreibverstärker aktiviert und in Abhängigkeit des Eingangsdatums die eine Emitterleitung auf hi- und die andere auf lo-Pegel gelegt. Ausgehend von einem gesperrten Transistor T2 und leitendem T1 kippt dieses FF, wenn am Emitter von T2 (Anschluß D) ein lo-Potential anliegt. Durch den hi-Pegel an allen drei Emitteranschlüssen des

Bulme Graz Seite 34

Transistors T1 sperrt dieser. Dadurch stellt sich ein hohes Basispotential an T2 ein, folglich leitet jetzt dieser Transistor.

Bipolare TTL-RAMs wurden in der Vergangenheit wegen der kurzen Zugriffszeiten (<100ns) bei schnellen Schaltungen eingesetzt. Durch den großen Flächenbedarf der Bipolartransistoren und die hohe Verlustleistung ist die Speicherkapazität begrenzt (<4kbit).

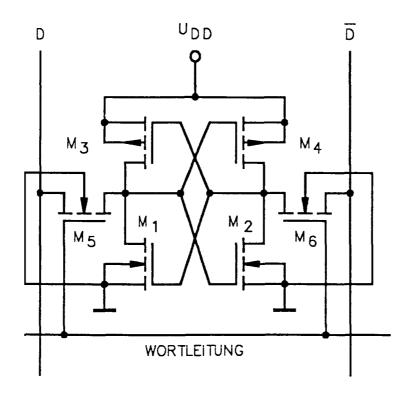

#### 7.3.2 CMOS-Speicherzelle:

CMOS - RAM mit sechs Transistoren

Bei einem CMOS-RAM findet man im allgemeinen sechs Transistor-Speicherzellen. Die Speicherzelle wird durch die beiden rückgekoppelten CMOS-Inverter mit den Transistoren M1 bis M4 gebildet. Wenn M1 und M4 leiten, sperren M2 und M3. Durch die anliegende Adresse wird vom Zeilendekoder eine Zeile, die als "Wortleitung" bezeichnet wird, aktiviert. Die von der Wortleitung mit einem hi-Pegel angesteuerten Schalttransistoren M5 und M6 legen beim Lesen die Drainpotentiale der N-Kanal-Transistoren auf die beiden Spaltenleitungen, die als Bitleitungen (D und  $\overline{D}$ ) bezeichnet werden. Diese Bitleitungen werden einem Spaltenmultiplexer zugeführt, der das durch die Adresse selektierte Bitleitungspaar auf den Leseverstäreker legt und zum Ausgang führt.

Beim Schreibvorgang arbeitet der Multiplexer als Dekoder/Demultiplexer. Das Datum liegt in identischer und invertiert Form an den beiden selektierten Bitleitungen. Die gewünschte Speicherzelle wird durch Dekodierung der Wortleitung selektiert. Liegt z.B. an der Bitleitung D ein lo-Pegel und sperrt M1, so erzwingt der eingeschaltete Transistor M5, daß der zuvor leitende Transistor M2 sperrt und M1 leitet.

### 7.3.3 Symbole für Impuls- bzw. Zeitdiagramme:

| SYMBOL | EINGANG                    | AUSGANG                        |

|--------|----------------------------|--------------------------------|

|        | Muß konstant H oder L sein | Ist konstant H oder L          |

|        | Wechsel ist erlaubt        | Wechsel findet statt           |

|        | H/L - Wechsel ist erlaubt  | H/L - Wechsel findet statt     |

|        | L/H - Wechsel ist erlaubt  | L/H - Wechsel findet statt     |

|        | Ohne Bedeutung             | Unbekannt oder wechselnd       |

|        |                            | Tristate (hochohmiger Zustand) |

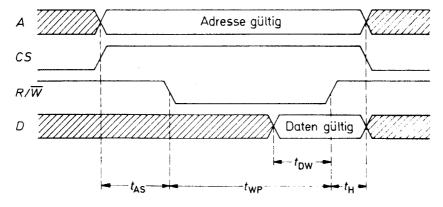

### 7.3.4 Zeitbedingungen:

Um die einwandfreie Funktion eines Speichers zu gewährleisten, müssen einige zeitliche Randbedingungen eingehalten werden. Um zu verhindern, daß die Daten in eine falsche Zelle geschrieben werden, darf der Schreibbefehl erst eine gewisse Zeit nach der Adresse angelegt werden. Diese Zeit heißt Adress Setup Time  $t_{AS}$ . Die Dauer eines Schreibimpulses darf den Minimalwert  $t_{WP}$  (Write Pulse Width) nicht unterschreiten.

Zeitlicher Ablauf eines Schreibvorganges

$t_{AS}$ : Address Setup Time  $t_{WP}$ : Write Pulse Width

t<sub>DW</sub>: Data Valid to End of Write Time

$t_{\rm H}$ : Hold Time

Die Daten werden am Ende des Schreibimpulses eingelesen. Sie müssen eine bestimmte Mindestzeit vorher gültig, d.h. stabil sein. Diese Zeit heißt  $t_{\rm DW}$  (Data Valid to End of Write). Bei vielen Speichern müssen die Daten bzw. Adressen noch eine gewisse Zeit  $t_{\rm H}$  nach dem Ende des Schreibimpulses anliegen (Hold Time). Wie man aus dem Bild erkennt, ergibt sich für die Durchführung eines Schreibvorganges die Zeit:

Dies Summe dieser 4 Zeiten wird als Schreib-Zyklus-Zeit (Write Cycle Time) bezeichnet.

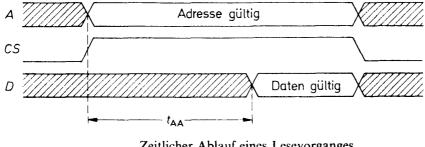

Der Lesevorgang ist im nächsten Bild dargestellt. Nach dem Anlegen der Adresse muß man die Zeit  $t_{AA}$  abwarten, bis die Daten am Ausgang gültig sind. Diese Zeit heißt Lese-Zugriffszeit (Adress Access Time) oder einfach Zugriffszeit.

Zeitlicher Ablauf eines Lesevorganges  $t_{AA}$ : Address Access Time

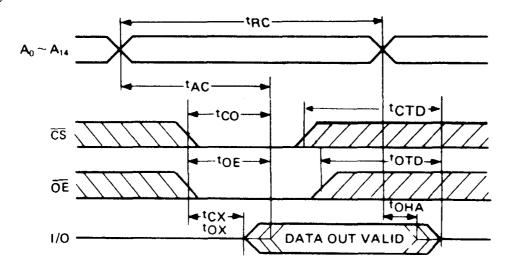

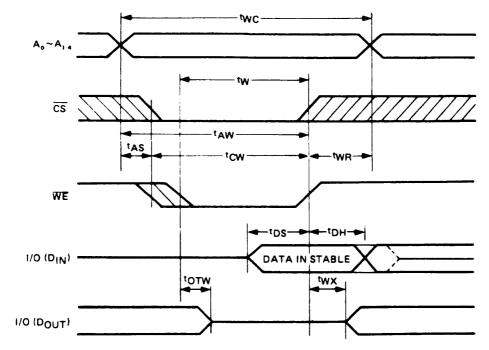

## 7.3.5 Beispiel aus dem Datenbuch:

## Lesezyklus:

# Tabelle für einen Lesezyklus:

| Parameter                               | Symbol           | MSM512 | Unit |      |      |      |      |    |

|-----------------------------------------|------------------|--------|------|------|------|------|------|----|

|                                         | 3911001          | Min.   | Max. | Min. | Max. | Min. | Max. |    |

| Read Cycle Time                         | tRC              | 85     |      | 100  |      | 120  |      | ns |

| Address Access Time                     | <sup>t</sup> AC  |        | 85   |      | 100  |      | 120  | ns |

| Chip Enable Access Time                 | tco              |        | 85   |      | 100  |      | 120  | ns |

| Output Enable to Output Valid           | <sup>t</sup> OE  |        | 45   |      | 50   |      | 60   | ns |

| Chip Selection to Output Active         | tCX              | 10     |      | 10   |      | 10   |      | ns |

| Output Hold Time From<br>Address Change | <sup>t</sup> OHA | 5      |      | 10   |      | 10   |      | ns |

| Output 3-state from Output Disable      | tOTD             |        | 30   |      | 35   |      | 35   | ns |

| Output 3-state from Chip<br>Deselection | tCTD             |        | 30   |      | 35   |      | 35   | ns |

| Output Enable to Output Active          | tox              | 5      |      | 5    |      | 5    |      | ns |

# Schreibzyklus:

Bulme Graz Seite 38

| lan                             | S               | MSM512 | 57ALL-85 | MSM512 | 57ALL-10 | MSM51257ALL-12 |      | l lada |

|---------------------------------|-----------------|--------|----------|--------|----------|----------------|------|--------|

| ltem                            | Symbol          | Min.   | Max.     | Min.   | Max.     | Min.           | Max. | Unit   |

| Write Cycle Time                | twc             | 85     |          | 100    |          | 120            |      | ns     |

| Address to Write Setup Time     | tAS             | 0      |          | 0      |          | 0              |      | ns     |

| Write Time                      | tw              | 70     |          | 75     |          | 90             |      | ns     |

| Write Recovery Time             | twn             | 5      |          | 10     |          | 10             |      | ns     |

| Data Setup Time                 | tDS             | 40     |          | 40     |          | 50             |      | ns     |

| Data Hold from Write Time       | <sup>t</sup> DH | 0      |          | 0      |          | 0              |      | ns     |

| Output 3-State from Write       | totw            | 0      | 30       | 0      | 35       | 0              | 35   | ns     |

| Chip Selection to End of Write  | tcw             | 75     |          | 90     |          | 100            |      | ns     |

| Address Valid to End of Write   | <sup>t</sup> AW | 75     |          | 90     |          | 100            |      | ns     |

| Output Active from End of Write | twx             | 5      |          | 5      |          | 5              |      | ns     |

# 7.4 Dynamische RAMs:

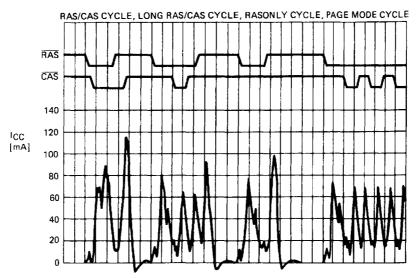

Dynamische RAMs weisen sehr hohe Speicherkapazitäten auf. Die hohe Integrationsdichte wird durch einen einfachen Datenspeicher, bestehend aus einer MOS-Kapazität von einigen Femtofarad Größe und einem Schalttransistor für die Bitleitung erreicht ("1 Transistorspeicher"). Die aufgebrachte Ladung in der Gate-Source-Kapazität dient zur Darstellung von einem bit. Allerdings bleibt diese Ladung nur für kurze Zeit erhalten. Deshalb muß der Kondensator regelmäßig (ca. alle 2..8ms) nachgeladen werden. Diesen Vorgang bezeichnet man als refresh, die Speicher als dynamische RAMs.

Diesem Nachteil stehen mehrere Vorteile gegenüber. Auf derselben Chipfläche, bei derselben Stromaufnahme und mit denselben Kosten läßt sich mit dynamischen RAMs ungefähr die vierfache Speicherkapazität realisieren.

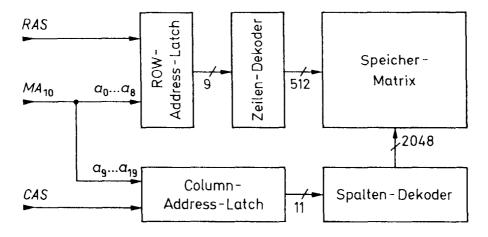

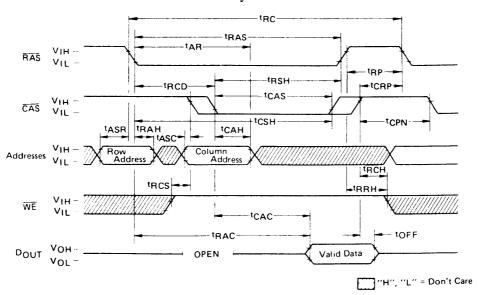

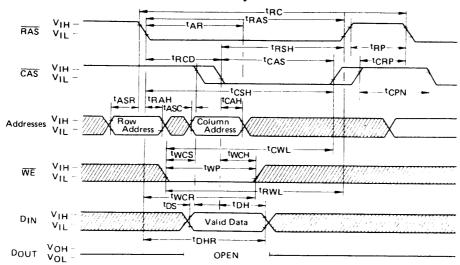

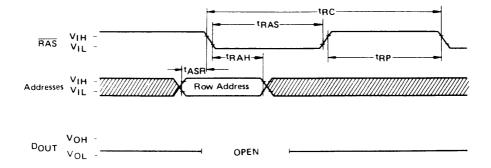

Um Anschlüsse einzusparen, wird die Adresse bei dynamischen RAMs in zwei Schritten eingegeben und im IC zwischengespeichert.

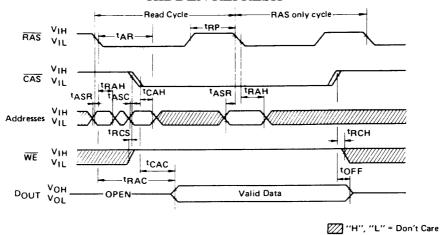

Adreß-Dekodierung in einem dynamischen 1 Mbit-Speicher

RAS: Row Address Strobe (gleichzeitig Chip Enable)

CAS: Column Address Strobe

Im ersten Schritt werden die Adressbits a<sub>0</sub> ... a<sub>8</sub> mit dem RAS-Signal in das Row-Adress-Latch gespeichert, und gleichzeitig das Bit a<sub>9</sub> im Column-Adress-Latch. Im zweiten Schritt werden die Adreßbits a<sub>10</sub> ... a<sub>19</sub> mit dem CAS-Signal in das Column-Adress-Latch geladen. Dadurch ist es möglich, einen 1Mbit-Speicher in einem 18poligen Gehäuse unterzubringen.

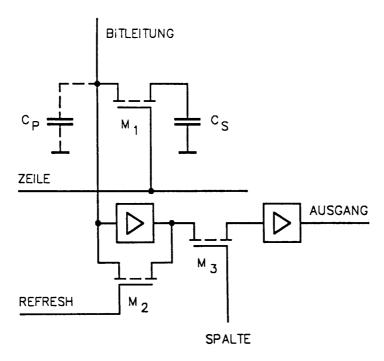

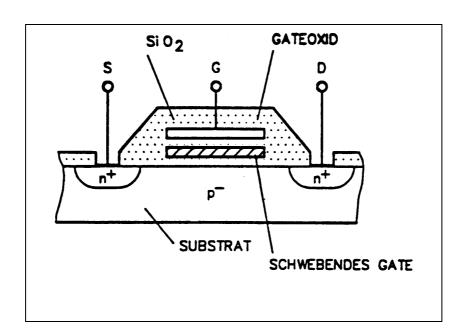

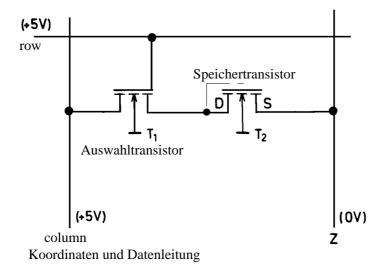

### 7.4.1 Speicherzellenaufbau:

Ist der Speicherkondensator  $C_S$  geladen, entspricht dies einer logischen "1" (hi-Pegel), ein nichtgeladener Konensator einer logischen "0" (lo-Pegel). Der Ladungsunterschied zwischen einem geladenen und einem ungeladenen Kondensator liegt bei etwa  $10^6$  Elektronen.

Über den Adreßdekoder wird nun eine Zeile (=Wortleitung) selektiert. Der hi-Pegel auf der Wortleitung steuert den Schalttransistor  $M_1$  durch und entlädt  $C_s$  wegen der hohen Parasitärkapazität Cp ( $C_p$  ca.  $10*C_s$ ). Dieser Ladungsausgleich bewirkt, daß die gespeicherte Information einer ganzen Zeile zerstört wird. Über einen Leseverstärker läßt sich das Signal an  $C_p$  verstärken.

Zum Auslesen wird über die Zeilenleitung der Transistor  $M_1$  durchgeschaltet. Der Ausgang des Leseverstärkers wird durch Schalten des selektierten Spaltentransistors  $M_3$  auf den Ausgangsverstärker geführt. Wegen der Ladungszerstörung ist eine Rückkopplung über  $M_2$  erforderlich, die das Signal am Kondensator wieder auffrischt (refresh). Der Speicherkondensator  $C_8$  wird über den Schalttransistor  $M_1$  von  $C_p$  geladen und somit auch aufgefrischt.

Während eines Refresh-Vorganges wird M<sub>3</sub> nicht aktiviert. Bei einem Schreibvorgang wird eine Bitleitung durch den Adreßdekoder selektiert und dadurch die zugehörige parasitäre Kapazität

$C_p$  geladen. Über die selektierte Wortleitung (Zeile) wird die Ladung über  $M_1$  dem Speicherkondensator  $C_8$  zugeführt.

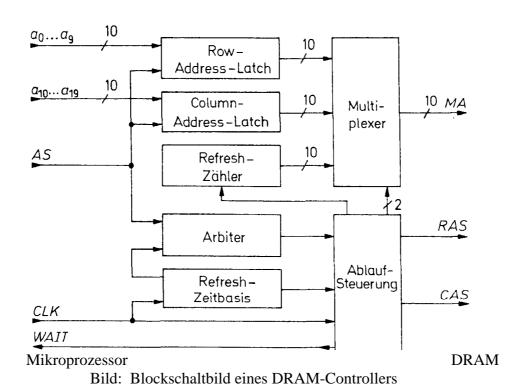

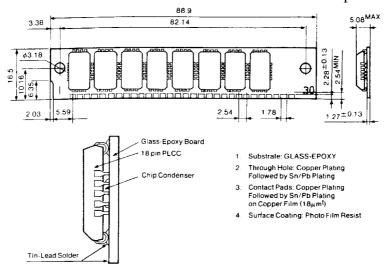

### 7.4.2 Dynamic RAM Controller:

Der Betrieb von dynamischen RAMs erfordert zusätzliche Schaltungen. Bei einem normalen Speicherzugriff muß die Adresse in zwei aufeinanderfolgenden Schritten in das RAM geladen werden. Um einen Datenverlust zu vermeiden, ist es erforderlich, alle Zeilenadressen in (normalerweise) 8 ms mindestens einmal aufzurufen. Wenn der Speicherinhalt nicht zyklisch ausgelesen wird, sind Schaltungszusätze notwendig, die eine zyklische Adressierung zwischen den normalen Speicherzugriffen bewirken. Man bezeichnet solche Zusatzschaltungen als "DYNAMIC-RAM-Controller".

Bei einem normalen Speicherzugriff wird die außen angelegte Adresse im ROM bzw. Column-Adress-Latch eingespeichert, wenn Adress-Strobe AS "hi" wird und damit anzeigt, daß die Adresse gültig ist. Gleichzeitig wird in der Ablaufsteuerung ein Zugriffszyklus ausgelöst. Dabei wird zunächst die Zeilenadresse a<sub>0</sub> ... a<sub>9</sub> über den Multiplexer an den Speicher ausgegeben. Dann wird der Row-Adress-Strobe gleich "hi" und bewirkt die Übernahme in den Speicher. Anschließend wird die Spaltenadresse a<sub>10</sub> ... a<sub>19</sub> ausgegeben und mit dem Column-Address-Strobe ebenfalls in den Speicher eingelesen. Nach der Adresseneingabe muß das Address-Strobe-Signal so lange auf "hi" bleiben, bis die Datenübertragung abgeschlossen ist. Der nächste Speicherzugriff darf nicht sofort erfolgen, sondern erst nach der "Precharge Time", die in derselben Größenordnung liegt wie die Zugriffszeit (Address Access Time). Zur Durchführung des Refreshs muß man die niedrigsten 512 Adressen alle 8 ms einmal anlegen. Bei einer "Refresh-Cycle-Time" von 300 ns ist dazu eine Gesamtzeit von ca. 150 us erforderlich. Die Verfügbarkeit des Speichers reduziert sich dadurch also um weniger als 2%. Bei der zeitlichen Aufteilung des Refreshs unterscheidet man drei verschiedene Methoden:

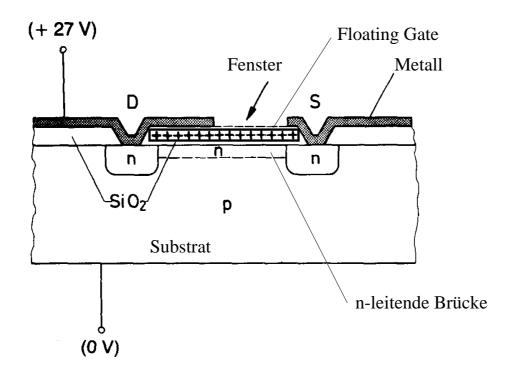

## Burst Refresh: